# INSTITUTO TECNOLÓGICO Y DE ESTUDIOS SUPERIORES DE OCCIDENTE

Reconocimiento de validez oficial de estudios de nivel superior según acuerdo secretarial 15018, publicado en el Diario Oficial de la Federación el 29 de noviembre de 1976.

Departamento de Electrónica, Sistemas e Informática

#### DOCTORADO EN CIENCIAS DE LA INGENIERÍA

# METODOLOGIAS DE OPTIMIZACION PARA ECUALIZADORES TRANSMISOR Y RECEPTOR DE ENLACES DE ALTA VELOCIDAD EN LA VALIDACION POST-SILICIO INDUSTRIAL DE PLATAFORMAS COMPUTACIONALES

Tesis que para obtener el grado de DOCTOR EN CIENCIAS DE LA INGENIERÍA presenta: Francisco Elías Rangel Patiño

Director de tesis: Dr. José Ernesto Rayas Sánchez Co-director de tesis: Dr. Nagib Hakim

Tlaquepaque, Jalisco. Julio de 2018

TÍTULO: Metodologías de Optimización para Ecualizadores

Transmisor y Receptor de Enlaces de Alta Velocidad en la

Validación Post-Silicio Industrial de Plataformas

Computacionales

**AUTOR:** Francisco Elías Rangel Patiño

Ingeniero en Comunicaciones y Electrónica (Universidad

Veracruzana, México)

Maestro en Electrónica y Telecomunicaciones (CICESE,

México)

Maestro en Ciencias Computacionales (TecNM, México)

**DIRECTOR DE TESIS:** José Ernesto Rayas Sánchez

Profesor Numerario del Departamento de Electrónica, Sistemas

e Informática, ITESO

Ingeniero en Electrónica (ITESO, México)

Maestro en Sistemas Electrónicos (ITESM Campus Monterrey,

México)

Doctor en Ingeniería Eléctrica (Universidad McMaster,

Canadá)

Senior, IEEE

**NÚMERO DE PÁGINAS:** xxx, 168

## ITESO - The Jesuit University of Guadalajara

Department of Electronics, Systems, and Informatics

DOCTORAL PROGRAM IN ENGINEERING SCIENCES

# TRANSMITTER AND RECEIVER EQUALIZERS OPTIMIZATION METHODOLOGIES FOR HIGH-SPEED LINKS IN INDUSTRIAL COMPUTER PLATFORMS POST-SILICON VALIDATION

Thesis to obtain the degree of DOCTOR IN ENGINEERING SCIENCES

Presents: Francisco Elías Rangel-Patiño

Thesis Director: Dr. José Ernesto Rayas-Sánchez Thesis Co-director: Dr. Nagib Hakim

> Tlaquepaque, Jalisco, Mexico July 2018

TITLE: Transmitter and Receiver Equalizers Optimization

Methodologies for High-Speed Links in Industrial

**Computer Platforms Post-Silicon Validation**

**AUTHOR:** Francisco Elías Rangel-Patiño

Bachelor's degree in electronics engineering (Universidad

Veracruzana, Mexico)

Master's degree in electrical engineering (CICESE, Mexico)

Master's degree in computer sciences (TecNM, Mexico)

**THESIS DIRECTOR:** José Ernesto Rayas-Sánchez

Department of Electronics, Systems, and Informatics, ITESO-

The Jesuit University of Guadalajara

Bachelor's degree in electronics engineering (ITESO, México)

Master's degree in electrical engineering (ITESM, México)

Ph.D. degree in electrical engineering (McMaster University,

Canada)

Senior, IEEE

**NUMBER OF PAGES:** xxx, 168

To my loving wife, Alma Delia, whose patience and understanding have made this achievement possible

#### Resumen

A medida que el diseño de microprocesadores se escala a tecnologías nanométricas, las técnicas tradicionales de validación post-silicio resultan inadecuadas para lograr una cobertura funcional completa del sistema. Complejidades físicas del diseño, y variaciones extremas en los procesos tecnológicos, crean grandes desafíos para garantizar que el sistema funcione adecuadamente en las variantes condiciones de proceso de manufactura, voltaje y temperatura (PVT). Adicionalmente, cada vez hay un número mayor de circuitos de señal mixta en los microprocesadores. Una parte importante de ellos corresponde a los enlaces de entrada/salida de alta velocidad (HSIO; por sus siglas en inglés). Mejoras en el diseño de circuitos, en el procesamiento de señales y en los procesos de manufactura, han permitido que las velocidades de las interfaces HSIO rebasen los 10 Gb/s. Los efectos de ruido no deseado pueden crear múltiples problemas de integridad de señal, lo cual se agrava por el continuo incremento de las velocidades de canal al pasar de una generación tecnológica a la siguiente. Resulta evidente que los retos de la validación post-silicio están en constante aumento, aunados a una alta presión por mantener calendarios agresivos de lanzamiento al mercado. Con todos estos elementos, la validación postsilicio de los enlaces HSIO es complicada y extensa, además de ser crítica en la toma de decisión para el lanzamiento de un producto al mercado. Uno de los mayores desafíos radica en el proceso de sintonización de la capa física, donde se utilizan técnicas de ecualización para cancelar efectos indeseados inducidos por los canales. Ajustar la ecualización del transmisor (Tx) y del receptor (Rx) en PVT, considerando diferentes interconexiones de canal, es una tarea demandante en la validación post-silicio. Las prácticas industriales actuales para sintonización de la capa física requieren mediciones de laboratorio masivas, ya que se basan en métodos de enumeración exhaustiva, convirtiendo el proceso de ecualización en una tarea prolongada y prácticamente prohibitiva bajo las restricciones de lanzamiento al mercado. En esta tesis doctoral se proponen métodos de optimización directa, de modelaje sustituto y mapeo espacial, combinados con funciones objetivo apropiadas, para sintonizar eficientemente los ecualizadores del Tx y Rx. La evaluación de los métodos es realizada mediante mediciones de laboratorio en plataformas industriales realistas. Los resultados obtenidos demuestran la eficacia de los métodos propuestos, así como una mejora sustancial en desempeño, con respecto a la práctica industrial actual.

# **Summary**

As microprocessor design scales to nanometric technology, traditional post-silicon validation techniques are inappropriate to get a full system functional coverage. Physical complexity and extreme technology process variations introduce design challenges to guarantee performance over process, voltage, and temperature (PVT) conditions. In addition, there is an increasingly higher number of mixed-signal circuits within microprocessors. A significant portion of them corresponds to high-speed input/output (HSIO) links. Improvements in signaling methods, circuits, and process technology have allowed HSIO data rates to scale beyond 10 Gb/s. Undesired noise effects can create multiple signal integrity problems. This problem is aggravated by the fact that channel speeds keep increasing from one generation bus technology to the next one. It is evident that challenges of post-silicon validation are continuously increasing, along with a high pressure of maintaining aggressive launch schedules. With all of these elements, post-silicon validation of HSIO links is tough and time-consuming, and can be critical for making a product release qualification decision. One of the major challenges in electrical validation of HSIO links lies in the physical layer (PHY) tuning process, where equalization techniques are used to cancel undesired effects induced by the channels. Adjusting the transmitter (Tx) and receiver (Rx) equalization across PVT and different interconnect channels can be a very time-consuming task in post-silicon validation. Typical current industrial practices for PHY tuning require massive lab measurements, since they are based on exhaustive enumeration methods, making the equalization process too lengthy and practically prohibitive under current silicon time-to-market commitments. In this doctoral dissertation, direct and surrogate-based optimization methods, including space mapping, are proposed based on suitable objective functions to efficiently tune the Tx and Rx equalizers. The proposed methodologies are evaluated by lab measurements on realistic industrial post-silicon validation platforms, demonstrating the efficiency of the proposed methods and substantial performance improvements as compared with those achieved by current industrial practices.

## Acknowledgements

The author wishes to express his sincere appreciation to Dr. José Ernesto Rayas-Sánchez, professor of the Department of Electronics, Systems, and Informatics at ITESO, and director of research in the Computer-Aided Engineering of Circuits and Systems (CAECAS) group at ITESO, for his encouragement, expert guidance, and keen supervision as doctoral thesis director throughout the course of this work. The author offers his gratitude to Dr. Nagib Hakim, Principal Engineer from Intel Corporation, for his support as doctoral thesis co-director during the development of this work. He also thanks Dr. Zabdiel Brito-Brito, Dr. Arturo Veloz-Guerrero, Dr. José Rodrigo Camacho-Pérez, and Dr. Manuel Salim-Maza, members of his Ph.D. Thesis Committee, for their interest, assessment, and suggestions.

The author has greatly benefited from working with MATLAB, developed by The MathWorks Inc.

Special thanks are due to Dr. Zabdiel Brito-Brito, from CAECAS research group at ITESO, and Mr. Edgar A. Vega-Ochoa, from Intel Corporation, for fruitful cooperation and helpful technical discussions.

It is the author's pleasure to acknowledge fruitful collaboration and stimulating discussions with his colleagues of CAECAS research group at ITESO – The Jesuit University of Guadalajara: Andrés Viveros-Watcher, Felipe de Jesús Leal-Romo, José Luis Chávez-Hurtado, and Rafael del-Rey-Acuña, as well as with colleagues at Intel Corp.: Alejandro Cortez-Ibarra, Brenda M. Marcial-Camacho, Carolina Olea-Gutierrez, Carlos Galindo-Meza, Carlos Rivas-Parra, Jesus Gomez-Lopez, Miguel Davalos-Santana, Ricardo Chavez-Cuadras, Ricardo Baca-Baylon, Rodrigo Camacho-Perez, and Vicente Penney.

The author gratefully acknowledge the financial assistance through a scholarship granted by the *Consejo Nacional de Ciencia y Tecnología* (CONACYT), Mexican Government, as well as the financial support provided by Intel Corporation.

Finally, special thanks are due to my family: my wife Alma Delia, and my children Perla and Yasmin, for their understanding, patience, and continuous loving support.

# Contenido

| Re  | sumo   | en                                                       | vii  |

|-----|--------|----------------------------------------------------------|------|

| Su  | mma    | ry                                                       | ix   |

| Re  | cono   | cimientos                                                | xi   |

| Co  | nten   | ido                                                      | xiii |

| Со  | nteni  | ts                                                       | xix  |

| Lis | sta de | e Figuras                                                | XXV  |

| Lis | sta de | e Acrónimos                                              | xxix |

| Int | trodu  | ıcción                                                   | 1    |

| 1.  | Val    | idación Post-Silicio                                     | 7    |

|     | 1.1.   | Introducción                                             | 7    |

|     | 1.2.   | VALIDACIÓN DE SILICIO                                    | 9    |

|     |        | 1.2.1 Pre-Silicio y Post-Silicio                         | 9    |

|     |        | 1.2.2 Disciplinas de Validación Post-Silicio             | 11   |

|     |        | 1.2.3 Validación Eléctrica Post-Silicio                  | 12   |

|     | 1.3.   | VALIDACIÓN DE LOS MÁRGENES DEL SISTEMA – EL CONCEPTO SMV | 12   |

|     | 1.4.   | RETOS EN LA VALIDACIÓN POST-SILICIO                      | 14   |

|     |        | 1.4.1 Desarrollo de Silicio                              | 14   |

|     |        | 1.4.2 Tiempo para Calificación                           | 14   |

|     |        | 1.4.3 Limitado Número de Pruebas                         | 16   |

|     |        | 1.4.4 Limitado Número de Partes                          | 17   |

|     |        | 1.4.5 Interacción Compleja con Circuitos Circundantes    | 17   |

|     |        | 1.4.6 Reproducción de Fallas                             | 17   |

|     |        | 1.4.7 Simulación a Nivel Sistema                         | 17   |

#### CONTENIDO

|    |      | 1.4.8 Sintonización en Post-Silicio                                     | 18 |

|----|------|-------------------------------------------------------------------------|----|

|    | 1.5. | OPORTUNIDADES EN LA VALIDACIÓN ELÉCTRICA POST-SILICIO                   | 18 |

|    |      | 1.5.1 Conectando Verificación Pre-Silicio y Validación Post-Silicio     | 19 |

|    |      | 1.5.2 Compensaciones entre Tiempo de Validación y Calidad               | 19 |

|    |      | 1.5.3 Integrando Múltiples Fuentes de Datos                             | 20 |

|    |      | 1.5.4 Conectando Simulación con Validación                              | 20 |

|    | 1.6. | Conclusiones                                                            | 21 |

| 2. | Ecu  | alización de Canal para Enlaces Seriales de Alta Velocidad              | 23 |

|    | 2.1. | Introducción                                                            | 23 |

|    | 2.2. | Interferencia Entre-Símbolos (ISI)                                      | 24 |

|    | 2.3. | Concepto de Ecualización                                                | 25 |

|    | 2.4. | ECUALIZACIÓN EN EL TRANSMISOR                                           | 27 |

|    | 2.5. | ECUALIZACIÓN EN EL RECEPTOR                                             | 29 |

|    |      | 2.5.1 Ecualizador Lineal de Tiempo Continuo (CTLE)                      | 29 |

|    |      | 2.5.2 Ecualizador de Decisión Retroalimentada (DFE)                     | 30 |

|    | 2.6. | ALGORITMO PARA ECUALIZADORES ADAPTIVOS                                  | 31 |

|    | 2.7. | CONCLUSIONES                                                            | 32 |

| 3. | Val  | idación de los Márgenes del Sistema                                     | 35 |

|    | 3.1. | Introducción                                                            | 35 |

|    | 3.2. | Margen de Operación                                                     | 37 |

|    | 3.3. | Instrumentos Embebidos                                                  | 37 |

|    | 3.4. | Pruebas de Lazo Cerrado                                                 | 39 |

|    | 3.5. | PRUEBAS DE INTERCONEXIÓN A NIVEL SISTEMA                                | 40 |

|    |      | 3.5.1 Pruebas de Interconexión con Escaneo de Limites                   | 41 |

|    |      | 3.5.2 Pruebas de Interconexión con Escaneo de Limites en Alta Velocidad | 41 |

|    |      | 3.5.3 Autodiagnóstico de Interconexión                                  | 42 |

|    | 3.6. | Prueba Funcional Utilizando Instrumentos Embebidos                      | 44 |

|    |      | 3.6.1 Prueba de Márgenes                                                | 46 |

|    | 37   | Conclusiones                                                            | 48 |

| 4. |      | alización del Receptor HSIO por medio de Optimización con delo Sustitutodelo Sustituto | 51      |

|----|------|----------------------------------------------------------------------------------------|---------|

|    | 4.1. | Introducción                                                                           | 51      |

|    | 4.2. | SISTEMA DE MEDICIONES                                                                  | 53      |

|    |      | 4.2.1 Márgenes del Sistema                                                             | 54      |

|    |      | 4.2.2 Pruebas de Tolerancia al Ruido                                                   | 54      |

|    | 4.3. | FORMULACIÓN DE LA FUNCIÓN OBJETIVO                                                     | 58      |

|    |      | 4.3.1 Función Objetivo de Márgenes del Sistema                                         | 58      |

|    |      | 4.3.2 Función Objetivo de Márgenes del Sistema y Tolerancia al Ruido                   | 61      |

|    | 4.4. | MODELO SUSTITUTO Y OPTIMIZACIÓN                                                        | 62      |

|    |      | 4.4.1 Diseño de Experimentos                                                           | 62      |

|    |      | 4.4.2 Sucesión de Baja Discrepancia                                                    | 63      |

|    |      | 4.4.3 Secuencia Sobol                                                                  | 64      |

|    |      | 4.4.4 Modelo Sustituto Kriging                                                         | 65      |

|    |      | 4.4.5 Optimización usando Modelo Sustituto                                             | 67      |

|    | 4.5. | CASOS DE PRUEBA                                                                        | 68      |

|    |      | 4.5.1 Caso de Prueba 1: USB3                                                           | 69      |

|    |      | 4.5.2 Caso de Prueba 2: SATA3                                                          | 71      |

|    |      | 4.5.3 Caso de Prueba 3: PCIe                                                           | 73      |

|    | 4.6. | Conclusiones                                                                           | 73      |

| 5. |      | alización del Transmisor Ethernet por medio de Optimización ecta                       | 75      |

|    | 5.1. | Introducción                                                                           | 75      |

|    | 5.2. | BANCO DE PRUEBAS DEL SISTEMA                                                           | 77      |

|    | 5.3. | SISTEMA DE MEDICIONES                                                                  | 78      |

|    | 5.4. | FORMULACIÓN DE LA FUNCIÓN OBJETIVO Y OPTIMIZACIÓN                                      | 79      |

|    | 5.5. | RESULTADOS                                                                             | 81      |

|    | 5.6. | CONCLUSIONES                                                                           | 82      |

| 6. | Ecu  | alización del Transceptor PCIe por medio de Optimización Direc                         | ta . 85 |

|    | 6.1. | Introducción                                                                           | 85      |

#### CONTENIDO

|    | 6.2. | ECUALIZACIÓN PCI EXPRESS                                  | 88  |

|----|------|-----------------------------------------------------------|-----|

|    |      | 6.2.1 Ecualizadores Tx y Rx                               | 88  |

|    |      | 6.2.2 Proceso de Ecualización                             | 89  |

|    | 6.3. | MATRIZ DE COEFICIENTES DE ECUALIZACIÓN EN EL TRANSMISOR   | 90  |

|    | 6.4. | FORMULACIÓN DE LA FUNCIÓN OBJETIVO Y OPTIMIZACIÓN         | 92  |

|    | 6.5. | BANCO DE PRUEBAS DEL SISTEMA                              | 95  |

|    | 6.6. | RESULTADOS                                                | 96  |

|    | 6.7. | CONCLUSIONES                                              | 98  |

| 7. | Mo   | delado Sustituto Burdo del Receptor HSIO                  | 99  |

|    | 7.1. | Introducción                                              | 99  |

|    | 7.2. | MÁQUINA DE APRENDIZAJE EN VALIDACIÓN POST-SILICIO         | 101 |

|    | 7.3. | CONCEPTOS BÁSICOS DE REDES NEURONALES ARTIFICIALES        | 103 |

|    |      | 7.3.1 Neuronas Artificiales                               | 103 |

|    |      | 7.3.2 Topologías de ANN                                   | 104 |

|    | 7.4. | Modelado del Receptor por medio de ANN                    | 105 |

|    |      | 7.4.1 Topología ANN                                       | 106 |

|    |      | 7.4.2 Modelado por Descomposición                         | 107 |

|    |      | 7.4.3 Modelado y Entrenamiento de ANN                     | 108 |

|    | 7.5. | CONFIGURACIÓN DEL SISTEMA EXPERIMENTAL Y MÉTODOS DOE      | 110 |

|    | 7.6. | RESULTADOS DEL MODELADO NEURAL                            | 113 |

|    | 7.7. | CONCLUSIONES                                              | 115 |

| 8. |      | ualización del Receptor HSIO por Medio de Optimización de | -   |

|    | Esp  | acial                                                     | 117 |

|    | 8.1. | Introducción                                              | 117 |

|    | 8.2. | MAPEO ESPACIAL BASADO EN BROYDEN                          | 119 |

|    |      | 8.2.1 Modelo Fino                                         | 119 |

|    |      | 8.2.2 Modelo Burdo                                        | 120 |

|    |      | 8.2.3 Función Objetivo                                    | 121 |

|    | 8.3. | OPTIMIZACIÓN ASM                                          | 121 |

|    | 8.4. | RESULTADOS DE OPTIMIZACIÓN                                | 123 |

|    | 8.5  | CONCLUSIONES                                              | 124 |

| Genera  | al Conclusions                              | 127 |

|---------|---------------------------------------------|-----|

| Conclu  | usiones Generales                           | 131 |

| Apénd   | lice                                        | 137 |

| A.      | LISTA DE REPORTES INTERNOS DE INVESTIGACIÓN | 139 |

| B.      | LISTA DE PUBLICACIONES                      | 141 |

|         | B.1. Artículos de Revista                   | 141 |

|         | B.2. Artículos de Congresos                 | 141 |

|         | B.3. Artículos de congresos INTEL           | 143 |

| Bibliog | grafía                                      | 145 |

| Índice  | de Autores                                  | 159 |

| Índice  | de Términos                                 | 165 |

# **Contents**

| Re  | sumo    | en                                                  | vii  |

|-----|---------|-----------------------------------------------------|------|

| Su  | mma     | ry                                                  | ix   |

| Ac  | knov    | vledgements                                         | xi   |

| Co  | nten    | ido                                                 | xiii |

| Co  | nten    | ts                                                  | xix  |

| Lis | st of ] | Figures                                             | XXV  |

| Lis | st of   | Acronyms                                            | xxix |

| In  | trodu   | ıction                                              | 1    |

| 1.  | Pos     | t-Silicon Validation                                | 7    |

|     | 1.1.    | Introduction                                        | 7    |

|     | 1.2.    | SILICON VALIDATION                                  | 9    |

|     |         | 1.2.1 Pre-Silicon and Post-Silicon                  | 9    |

|     |         | 1.2.2 Post-Silicon Validation Disciplines           | 11   |

|     |         | 1.2.3 Post-Silicon Electrical Validation            | 12   |

|     | 1.3.    | SYSTEM MARGINALITY VALIDATION – THE SMV CONCEPT     | 12   |

|     | 1.4.    | POST-SILICON VALIDATION CHALLENGES                  | 14   |

|     |         | 1.4.1 Silicon Development                           | 14   |

|     |         | 1.4.2 Time-to-Qualification                         | 14   |

|     |         | 1.4.3 Limited Number of Tests                       | 16   |

|     |         | 1.4.4 Limited Parts                                 | 17   |

|     |         | 1.4.5 Complex Interaction with Surrounding Circuits |      |

|     |         | 1.4.6 Failure Reproduction                          | 17   |

|     |         | 1.4.7 System-Level Simulation                       | 17   |

#### **CONTENTS**

|    |      | 1.4.8 Post-Silicon Tuning                                           | 18 |

|----|------|---------------------------------------------------------------------|----|

|    | 1.5. | POST-SILICON ELECTRICAL VALIDATION OPPORTUNITIES                    | 18 |

|    |      | 1.5.1 Bridging Pre-Silicon Verification and Post-Silicon Validation | 19 |

|    |      | 1.5.2 Trade-off between Validation Time and Quality                 | 19 |

|    |      | 1.5.3 Integrating Multiple Sources of Data                          | 20 |

|    |      | 1.5.4 Connecting Simulation with Validation                         | 20 |

|    | 1.6. | Conclusions                                                         | 21 |

| 2. | Cha  | annel Equalization for High-Speed Serial Links                      | 23 |

|    | 2.1. | Introduction                                                        | 23 |

|    | 2.2. | INTER-SYMBOL INTERFERENCE (ISI)                                     | 24 |

|    | 2.3. | EQUALIZATION CONCEPT                                                | 25 |

|    | 2.4. | EQUALIZATION AT THE TRANSMITTER                                     | 27 |

|    | 2.5. | EQUALIZATION AT THE RECEIVER                                        | 29 |

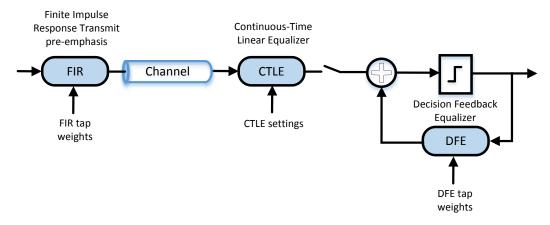

|    |      | 2.5.1 Continuous Time Linear Equalizer (CTLE)                       | 29 |

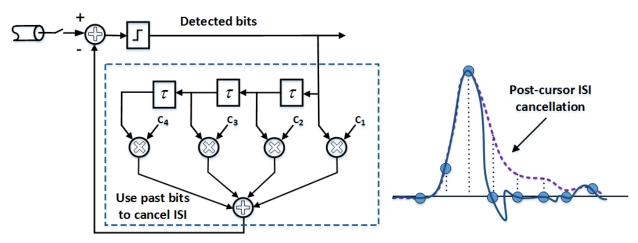

|    |      | 2.5.2 Decision Feedback Equalizer (DFE)                             | 30 |

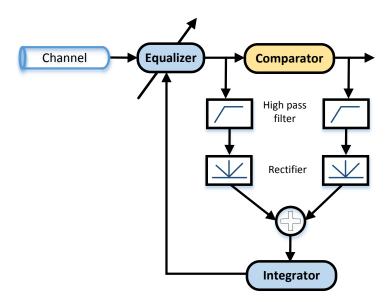

|    | 2.6. | ALGORITHMS FOR ADAPTIVE EQUALIZERS                                  | 31 |

|    | 2.7. | CONCLUSIONS                                                         | 32 |

| 3. | Sys  | tem Marginality Validation                                          | 35 |

|    | 3.1. | Introduction                                                        | 35 |

|    | 3.2. | OPERATING MARGIN                                                    | 37 |

|    | 3.3. | Embedded Instruments                                                | 37 |

|    | 3.4. | LOOPBACK TESTING                                                    | 39 |

|    | 3.5. | SYSTEM-LEVEL INTERCONNECT TESTING                                   | 40 |

|    |      | 3.5.1 Interconnect Testing with Boundary Scan                       | 41 |

|    |      | 3.5.2 Interconnect Testing with High-Speed Boundary Scan            | 41 |

|    |      | 3.5.3 Interconnect Built-In Self-Test                               | 42 |

|    | 3.6. | FUNCTIONAL TESTING BY USING EMBEDDED INSTRUMENTS                    | 44 |

|    |      | 3.6.1 Margin Testing                                                | 46 |

|    | 37   | CONCLUSIONS                                                         | 48 |

| 4. | HS   | O Receiver Equalization by Surrogate-Based Optimization            | 51 |

|----|------|--------------------------------------------------------------------|----|

|    | 4.1. | Introduction                                                       | 51 |

|    | 4.2. | System Measurements                                                | 53 |

|    |      | 4.2.1 System Margins                                               | 54 |

|    |      | 4.2.2 Jitter Tolerance Testing                                     | 54 |

|    | 4.3. | OBJECTIVE FUNCTION FORMULATION                                     | 58 |

|    |      | 4.3.1 Objective Function for System Margining                      | 58 |

|    |      | 4.3.2 Objective Function for System Margining and Jitter Tolerance | 61 |

|    | 4.4. | SURROGATE MODEL AND OPTIMIZATION                                   | 62 |

|    |      | 4.4.1 Design of Experiments                                        | 62 |

|    |      | 4.4.2 Low-discrepancy Sequences                                    | 63 |

|    |      | 4.4.3 The Sobol Sequence                                           | 64 |

|    |      | 4.4.4 Kriging Surrogate Model                                      | 65 |

|    |      | 4.4.5 Optimization using the Surrogate Model                       | 67 |

|    | 4.5. | TEST CASES                                                         | 68 |

|    |      | 4.5.1 Test Case 1: USB3                                            | 69 |

|    |      | 4.5.2 Test Case 2: SATA3                                           | 71 |

|    |      | 4.5.3 Test Case 3: PCIe                                            | 73 |

|    | 4.6. | CONCLUSIONS                                                        | 73 |

| 5. | Eth  | ernet Transmitter Equalization by Direct Optimization              | 75 |

|    | 5.1. | Introduction                                                       | 75 |

|    | 5.2. | System Test Setup                                                  | 77 |

|    | 5.3. | System Measurements                                                | 78 |

|    | 5.4. | OBJECTIVE FUNCTION FORMULATION AND OPTIMIZATION                    | 79 |

|    | 5.5. | RESULTS                                                            | 81 |

|    | 5.6. | Conclusions                                                        | 82 |

| 6. | PC   | le Transceiver Equalization by Direct Optimization                 | 85 |

|    | 6.1. | Introduction                                                       | 85 |

|    | 6.2. | PCI Express Equalization                                           | 88 |

|    |      | 6.2.1 Tx and Rx Equalizers                                         | 88 |

#### **CONTENTS**

|    |      | 6.2.2 Equalization Process                            | 89  |

|----|------|-------------------------------------------------------|-----|

|    | 6.3. | TRANSMITTER EQUALIZATION COEFFICIENT MATRIX           | 90  |

|    | 6.4. | OBJECTIVE FUNCTION FORMULATION AND OPTIMIZATION       | 92  |

|    | 6.5. | SYSTEM TEST SETUP                                     | 95  |

|    | 6.6. | RESULTS                                               | 96  |

|    | 6.7. | CONCLUSION                                            | 98  |

| 7. | HSI  | O Receiver Coarse Surrogates Modeling                 | 99  |

|    | 7.1. | Introduction                                          | 99  |

|    | 7.2. | MACHINE LEARNING IN POST-SILICON VALIDATION           | 101 |

|    | 7.3. | BASIC CONCEPTS ON ARTIFICIAL NEURAL NETWORKS          | 103 |

|    |      | 7.3.1 Artificial Neurons                              | 103 |

|    |      | 7.3.2 ANN Topologies                                  | 104 |

|    | 7.4. | ANN-Based Receiver Metamodeling                       | 105 |

|    |      | 7.4.1 ANN Topology                                    | 106 |

|    |      | 7.4.2 Decomposed Modeling                             | 107 |

|    |      | 7.4.3 ANN Modeling and Training                       | 108 |

|    | 7.5. | EXPERIMENTAL SYSTEM CONFIGURATION AND DOE APPROACHES  | 110 |

|    | 7.6. | NEURAL MODELING RESULTS                               | 113 |

|    | 7.7. | CONCLUSION                                            | 115 |

| 8. | HSI  | O Receiver Equalization by Space Mapping Optimization | 117 |

|    | 8.1. | Introduction                                          | 117 |

|    | 8.2. |                                                       |     |

|    |      | 8.2.1 Fine Model                                      | 119 |

|    |      | 8.2.2 Coarse Model                                    | 120 |

|    |      | 8.2.3 Objective Function                              | 121 |

|    | 8.3. | ASM OPTIMIZATION                                      | 121 |

|    | 8.4. | OPTIMIZATION RESULTS                                  | 123 |

|    | 8.5. | CONCLUSION                                            | 124 |

| Ge | nera | l Conclusions                                         | 127 |

| Conclusiones Generales |                                   |     |

|------------------------|-----------------------------------|-----|

| Appen                  | 137                               |     |

| A.                     | LIST OF INTERNAL RESEARCH REPORTS | 139 |

| B.                     | LIST OF PUBLICATIONS              | 141 |

|                        | B.1. Journal Papers               | 141 |

|                        | B.2. Conference Papers            | 141 |

|                        | B.3. INTEL Conference Papers      | 143 |

| Bibliog                | graphy                            | 145 |

| Autho                  | r Index                           | 159 |

| Subjec                 | rt Index                          | 165 |

# **List of Figures**

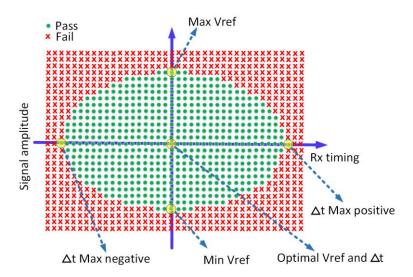

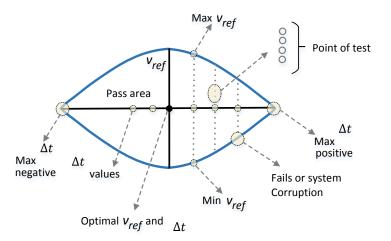

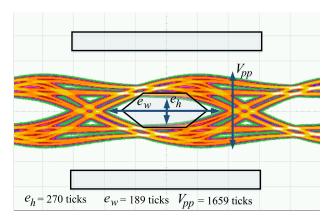

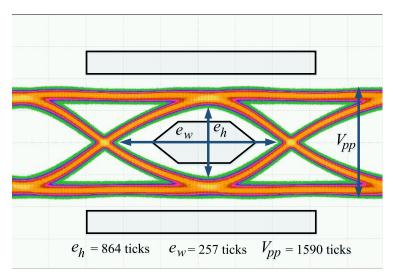

| Fig. 1.1 | Example of SMV functional eye diagram                                                                                                                                                                                          | 14 |

|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

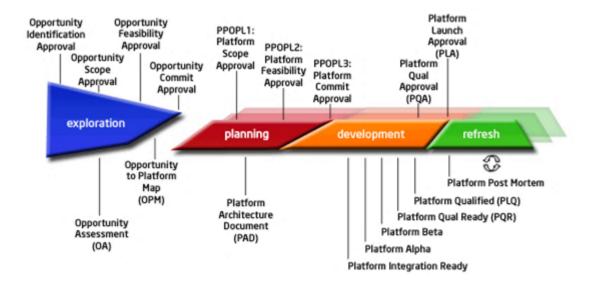

| Fig. 1.2 | Design and validation product lifecycle. Figure taken from [INTEL-03]                                                                                                                                                          | 15 |

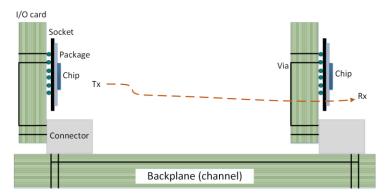

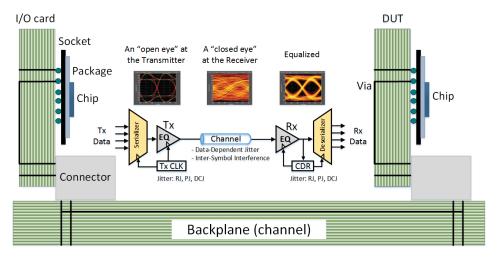

| Fig. 2.1 | Diagram of a typical backplane communication between two chips                                                                                                                                                                 | 24 |

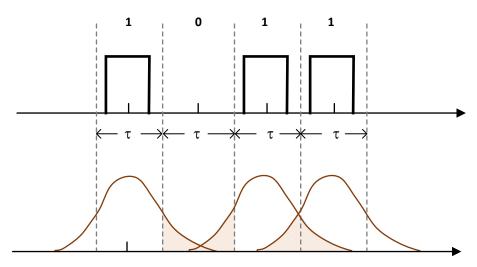

| Fig. 2.2 | Inter-symbol interference effect.                                                                                                                                                                                              | 25 |

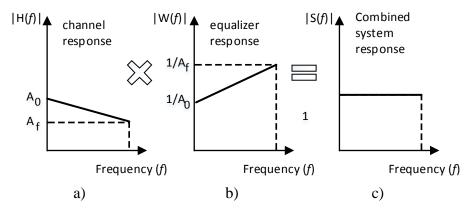

| Fig. 2.3 | Basic idea of equalization: the equalizer frequency response approximates the inverse of the channel frequency response to flatten out the overall response. a) channel response, b) equalizer response, c) equalized response | 26 |

| Fig. 2.4 | Graphical concept of the EQ process.                                                                                                                                                                                           | 27 |

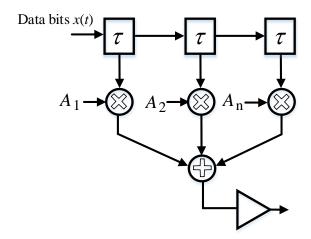

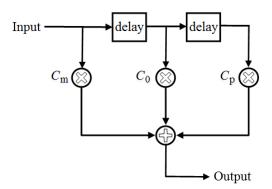

| Fig. 2.5 | Transmit pre-emphasis FIR filter                                                                                                                                                                                               | 28 |

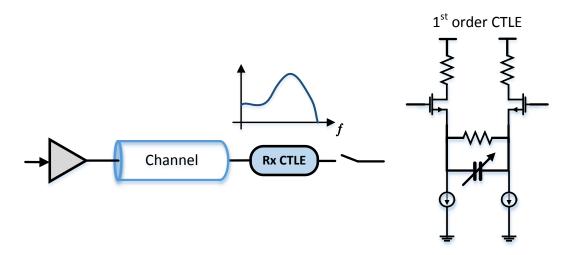

| Fig. 2.6 | Continuous time linear equalizer and typical transfer function                                                                                                                                                                 | 29 |

| Fig. 2.7 | Decision feedback equalizer.                                                                                                                                                                                                   | 30 |

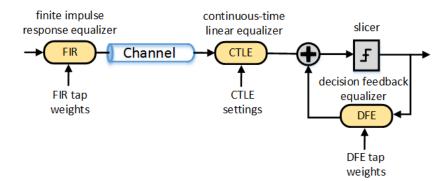

| Fig. 2.8 | Simultaneously employing Tx and Rx equalizers, combining different EQ topologies.                                                                                                                                              | 31 |

| Fig. 2.9 | Typical continuous-time adaptive equalizer.                                                                                                                                                                                    | 32 |

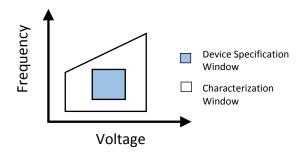

| Fig. 3.1 | Specification window and characterization window for electrical validation. Figure taken from [Gizopoulos-06].                                                                                                                 | 38 |

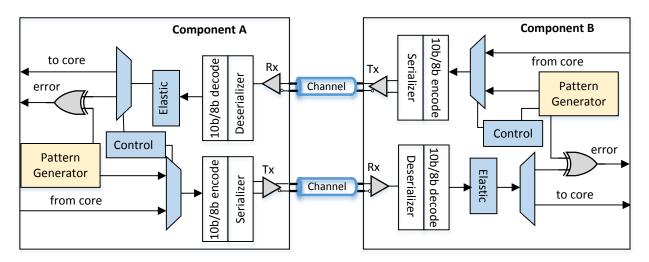

| Fig. 3.2 | IBIST as applied for high-speed serial testing at the board level. Figure taken from [Nejedlo-03].                                                                                                                             | 43 |

| Fig. 3.3 | Loopback mode testing.                                                                                                                                                                                                         | 45 |

| Fig. 3.4 | SMV's on-die instrumentation architecture.                                                                                                                                                                                     | 46 |

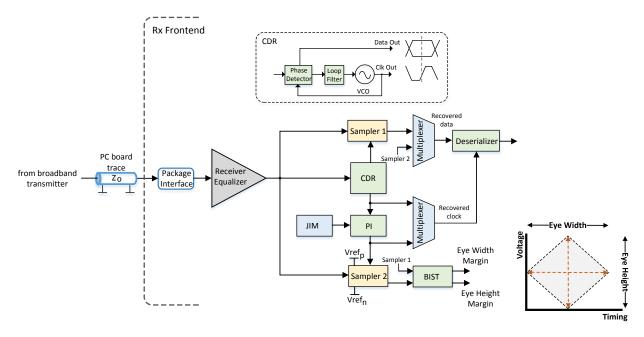

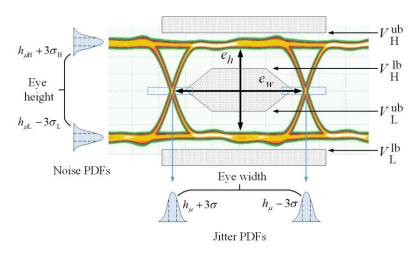

| Fig. 3.5 | Functional eye diagram based on multiple margin points.                                                                                                                                                                        | 47 |

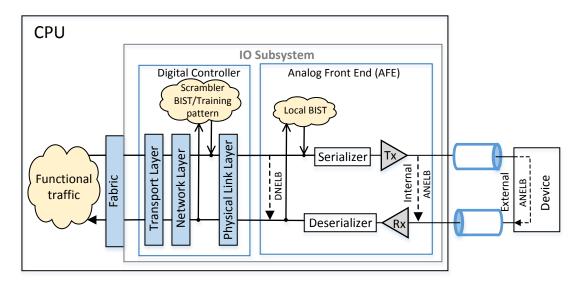

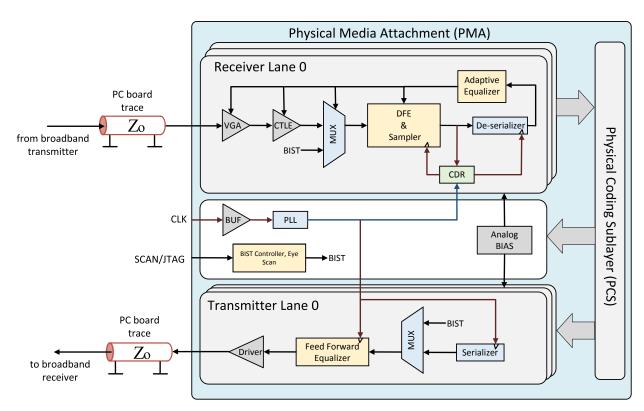

| Fig. 4.1 | Architecture of a typical SerDes PHY.                                                                                                                                                                                          | 53 |

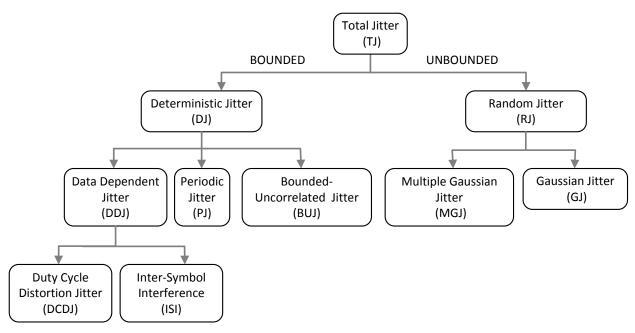

| Fig. 4.2 | Jitter classification and their relationships. Figure taken from [Wang-08]                                                                                                                                                     | 54 |

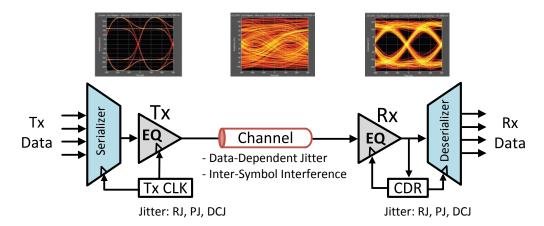

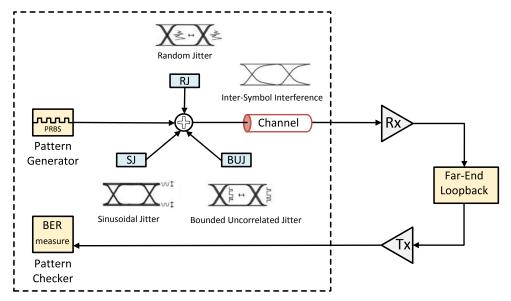

| Fig. 4.3 | Jitter sources in an HSIO link.                                                                                                                                                                                                | 55 |

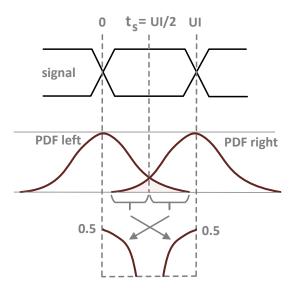

| Fig. 4.4 | Relationship between jitter and BER in the Rx. Figure taken from [Fan-09]                                                                                                                                                      | 56 |

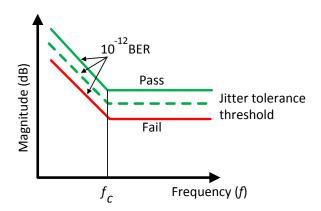

| Fig. 4.5 | Rx jitter tolerance threshold for testing. Figure taken from [Wang-08]                                                                                                                                                         | 57 |

| Fig. 4.6 | A generic test setup for Rx jitter testing.                                                                                                                                                                                    | 58 |

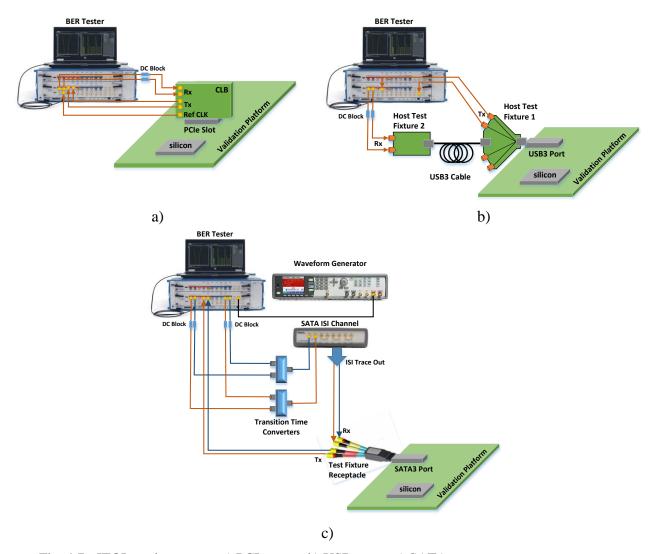

| Fig. 4.7 | JTOL testing setups: a) PCIe setup, b) USB setup, c) SATA setup                                                                                                                                                                | 59 |

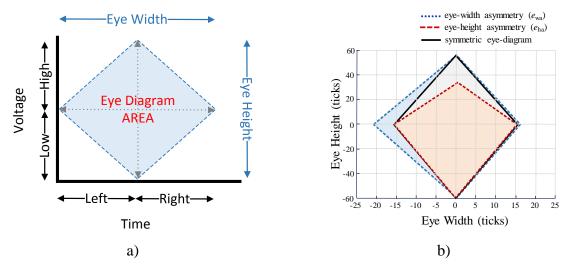

| Fig. 4.8 | Eye diagram: a) graphical objective function representation, b) example of asymmetries on 3 test cases of EQ.                                                                                                                  | 60 |

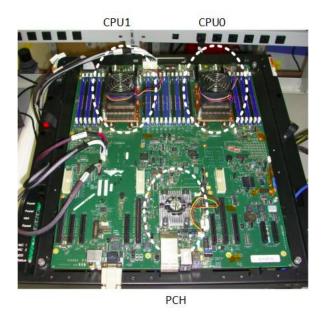

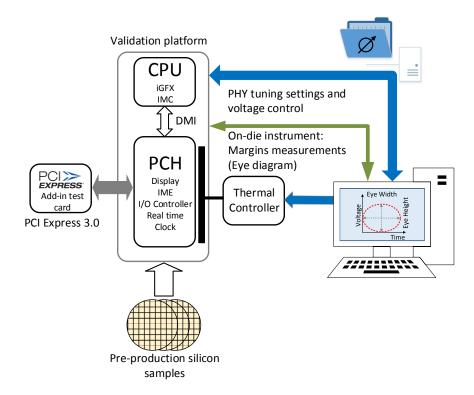

| Fig. 4.9 | Post-Silicon industrial validation platform.                                                                                                                                                                                   | 68 |

#### LIST OF FIGURES

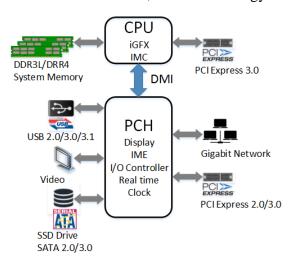

| Fig. 4.10 | Bock diagram of the platform controller hub                                                                                                                                                                             | . 68  |

|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

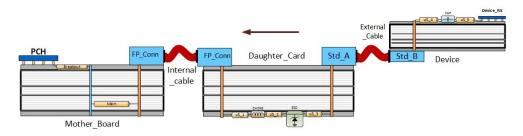

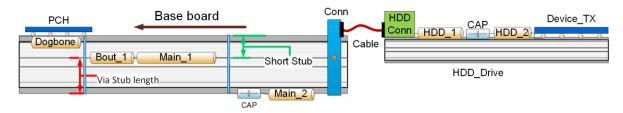

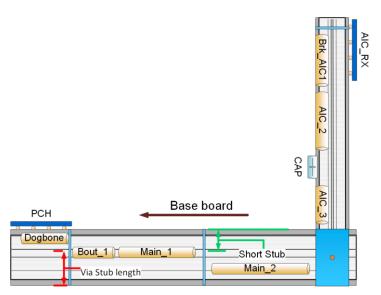

| Fig. 4.11 | USB3 Rx channel topology                                                                                                                                                                                                | . 69  |

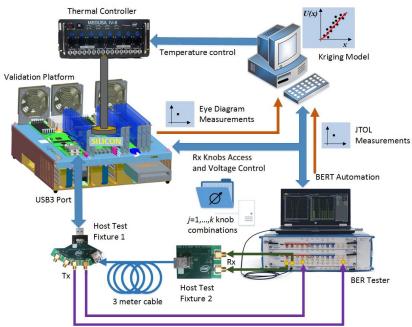

| Fig. 4.12 | The holistic methodology test setup for USB system margining and JTOL optimization.                                                                                                                                     | . 70  |

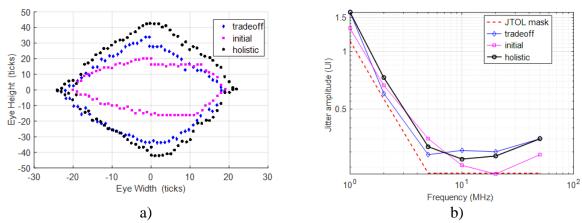

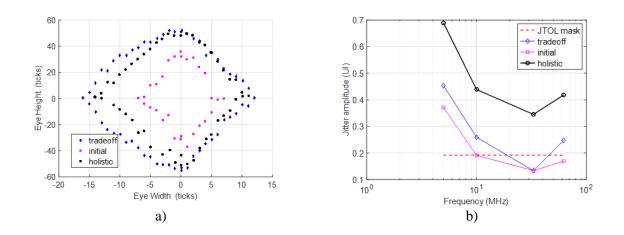

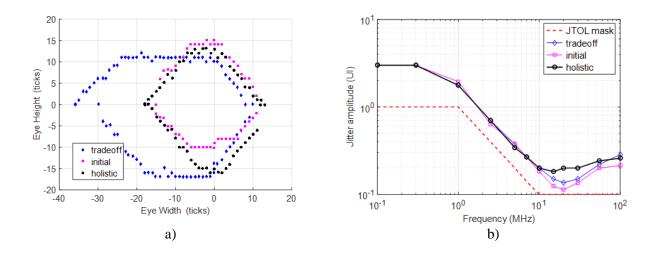

| Fig. 4.13 | USB3 results comparing the proposed methodology against the initial design and the trade-off approach: a) eye width versus eye height, b) JTOL testing results                                                          | . 70  |

| Fig. 4.14 | SATA Rx channel topology.                                                                                                                                                                                               | . 71  |

| Fig. 4.15 | SATA results comparing the proposed methodology against the initial design and the trade-off approach: a) eye width versus eye height, b) JTOL testing results.                                                         | 71    |

| Fig. 4.16 | PCIe Gen3 Rx channel topology.                                                                                                                                                                                          |       |

| Fig. 4.17 | PCIe results comparing the proposed methodology against the initial design and                                                                                                                                          | . , _ |

| 116. 1.17 | the trade-off approach: a) eye width versus eye height, b) JTOL testing results                                                                                                                                         | . 72  |

| Fig. 5.1  | Block diagram of a 3-tap transmit FIR filter                                                                                                                                                                            | . 76  |

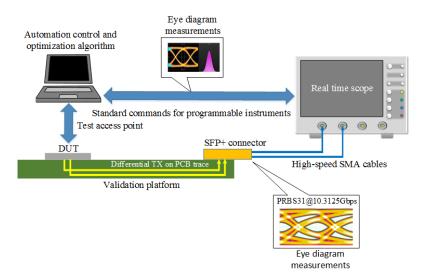

| Fig. 5.2  | Test setup for SFP transmitter optimization.                                                                                                                                                                            | . 77  |

| Fig. 5.3  | Eye diagram and SFP+ Tx mask.                                                                                                                                                                                           | . 78  |

| Fig. 5.4  | SFP eye diagram over mask before optimization.                                                                                                                                                                          | . 80  |

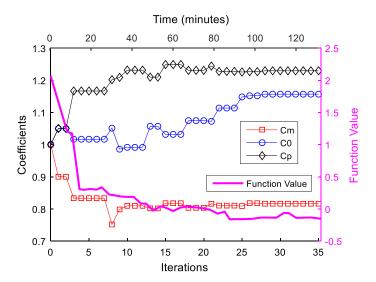

| Fig. 5.5  | SFP FIR normalized coefficients responses and function values across iterations.                                                                                                                                        |       |

|           |                                                                                                                                                                                                                         |       |

| Fig. 5.6  | SFP eye diagram over mask after optimization.                                                                                                                                                                           |       |

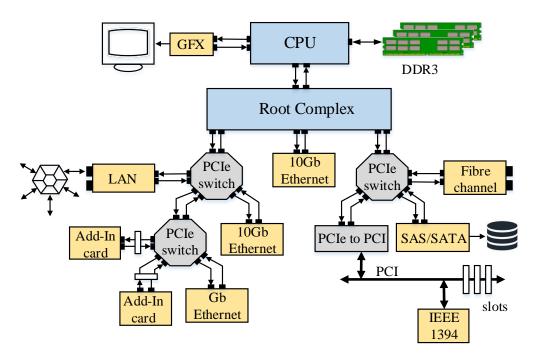

| Fig. 6.1  | PCIe switched architecture. Figure taken from [PCISIG-17]                                                                                                                                                               |       |

| Fig. 6.2  | A PCIe channel with Tx and Rx equalizers.                                                                                                                                                                               |       |

| Fig. 6.3  | PCIe Tx/Rx adaptive equalization.                                                                                                                                                                                       |       |

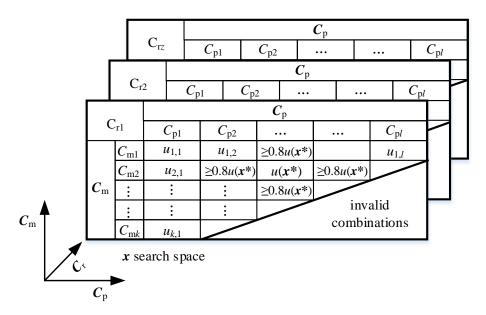

| Fig. 6.4  | PCIe EQ map coefficients search space for optimization.                                                                                                                                                                 | . 91  |

| Fig. 6.5  | PCI Express test setup: an Intel server post-silicon validation platform                                                                                                                                                | . 94  |

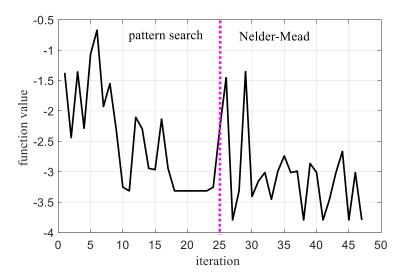

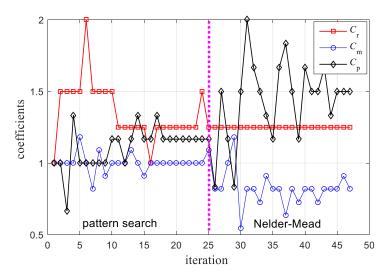

| Fig. 6.6  | PCIe objective function values across iterations                                                                                                                                                                        | . 96  |

| Fig. 6.7  | PCIe normalized coefficients responses across iterations                                                                                                                                                                | . 96  |

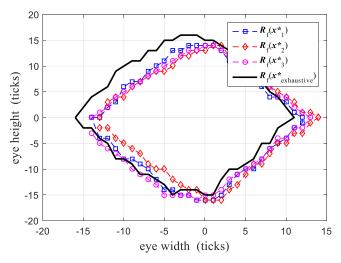

| Fig. 6.8  | PCIe eye diagram results: comparing the proposed methodology ( $R_f(x^*)$ ) with three different seeds against the exhaustive method ( $R_f(x^*_{exhaustive})$ )                                                        | . 97  |

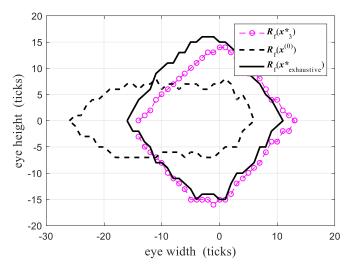

| Fig. 6.9  | PCIe eye diagram results: comparing the proposed methodology ( $\mathbf{R}_f(\mathbf{x}^*)$ ) against the initial design ( $\mathbf{R}_f^{(\mathbf{x}^0)}$ ) and the exhaustive method ( $\mathbf{R}_f(\mathbf{x}^*)$ ) | . 98  |

| Fig. 7.1  | Neural representations: a) simplified diagram of a biological neuron, b) inner-product artificial neuron (modified from [Rayas-Sánchez-15])                                                                             | 103   |

| Fig. 7.2  | ANN topologies: a) feedforward, b) recurrent. Figure taken from [Suzuki-11]                                                                                                                                             | 104   |

| Fig. 7.3  | ANN modeling concept. Figure modified from [Rayas-Sánchez-04].                                                                                                                                                          | 106   |

| Fig. 7.4  | A 3-layer perceptron including the scaling process. Figure modified from [Rayas-Sánchez-04]                                                                                                         |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Fig. 7.5  | ANN decomposed modeling. Figure modified from [Rayas-Sánchez-04] 109                                                                                                                                |

| Fig. 7.6  | Algorithm for training the ANN with controlled generalization performance 111                                                                                                                       |

| Fig. 7.7  | HSIO server post-silicon hardware configuration for Rx metamodeling 112                                                                                                                             |

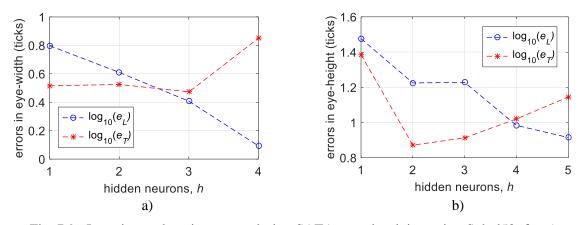

| Fig. 7.8  | Comparison of SATA neural model generalization performance for different DoE techniques: a) eye height error; b) eye width error                                                                    |

| Fig. 7.9  | Learning and testing errors during SATA neural training using Sobol50, for a) eye width and b) eye height                                                                                           |

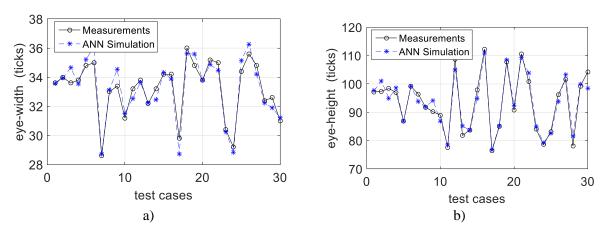

| Fig. 7.10 | Neural model generalization performance using Sobol50 for a) SATA eye width;<br>b) SATA eye height                                                                                                  |

| Fig. 7.11 | Neural model generalization performance using Sobol50 for a) USB width; and b) USB eye height                                                                                                       |

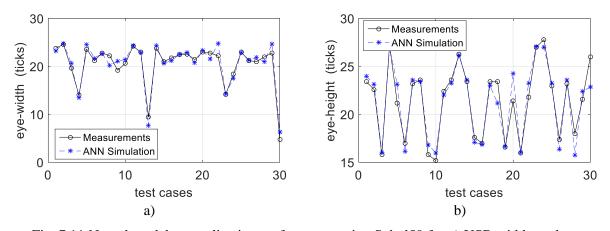

| Fig. 8.1  | HSIO link reconfiguration in post-silicon server validation to cancel out the effects of system channels' variability                                                                               |

| Fig. 8.2  | Test setup for SM optimization: an Intel server post-silicon validation platform 119                                                                                                                |

| Fig. 8.3  | Pseudo-code for the Broyden-based input space mapping optimization. Figure taken from [Rayas-Sánchez-11]                                                                                            |

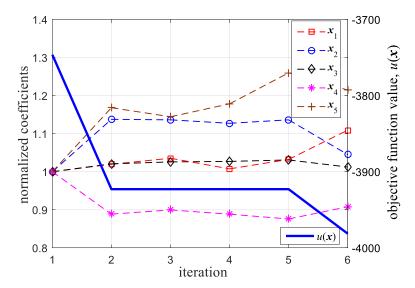

| Fig. 8.4  | Normalized SATA coefficients and objective function values across SM optimization iterations                                                                                                        |

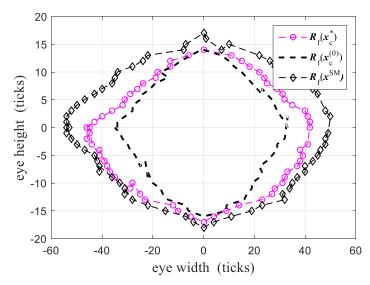

| Fig. 8.5  | Comparison between the system fine model responses at the initial Rx EQ coefficients, $x_c^{(0)}$ , at the optimal coarse model solution, $x_c^*$ , and at the spacemapped solution found, $x^{SM}$ |

|           |                                                                                                                                                                                                     |

# **List of Acronyms**

3LP 3-Layer Perceptron

ANN Artificial Neural Networks

ASIC Application-Specific Integrated Circuit

ASM Aggressive Space Mapping ATE Automatic Test Equipment

BER Bit-Error Rate

BIOS Basic Input Output System

BMF Bayesian Model Fusion

CAD Computer-Aided Design

CDR Clock Data Recovery

CMOS Complementary Metal–Oxide–Semiconductor

CPU Central Processing Unit

CTAE Continuous-Time Adaptive Equalizer

CTLE Continuous Time Linear Equalizer

CV Compatibility Validation

DAC Digital to Analog Converter

DFE Decision-Feedback Equalization

DFT Designed For Test

DFx Design-For-x

DIMM Dual In-Line Memory Module

DMA Direct Memory Access

DMI Direct Media Interface

DoE Design of Experiments

DUT Device-Under-Test

EM Electromagnetic

EQ Equalization

EV Electrical Validation

FFE Feed-Forward Equalizer

FIR Finite Impulse Response

FM Frequency Modulated

FS Full Swing

HSIO High-Speed Input/Output HVM High Volume Manufacturing IBIST Interconnect Built-In Self-Test

IC Integrated Circuit

IEEE Institute of Electrical and Electronics Engineers

IJATG Internal Joint Test Action Group

IL Insertion Loss

ISI Inter-Symbol Interference

JIM Jitter Injection Module

JTOL Jitter Tolerance

#### LIST OF ACRONYMS

LF Low Frequency

LMS Least Mean Squares

MAC Medium Access Control

MLP Multilayer Perceptrons

MSE Mean-Square Error

OS Operating System

PCH Platform Controller Hub

PCIe Peripheral Component Interconnect Express

PDF Probability Density Functions

PHY Physical Layer

PI Phase-Interpolator

PLL Phase-Locked Loop

PRBS Pseudo-Random Bit Sequence PRQ Product Release Qualification

PSM Polynomial-based Surrogate Modeling PVT Process, Voltage, and Temperature

RC Root Complex

RF Radio Frequency

RJ Random Jitter

Rx Receiver

SATA Serial Advanced Technology Attachment

SBO Surrogate-Based Optimization

SerDes Sserializer-Deserializer SFF Small Form Factor

SFP Small form-Factor Pluggable

SFP+ Enhanced SFP SJ Sinusoidal Jitter SM Space Mapping

SMA SubMiniature version A

SMV System Marginality Validation

SNR Signal-to-Noise Ratio

SoC Systems on Chip

SV System Validation

T&M Test and Measurement

TAP Test Access Port

TL Transmission Lines

TTM Time-To-Market

Tx Transmitter

UI Unit Interval

USB Universal Serial Bus

VGA Variable Gain Amplifier

VT Voltage/Temperature

ZF Zero Forcing

#### Introduction

A computer-aided design (CAD) tool based on electromechanical relays was programmed in the very early 1950's to solve the algebraic equilibrium-condition equations of a linear electrical network in the sinusoidal steady state [Graham-53]. Quickly it was possible to employ optimization techniques to achieve excellent designs of electric filters [Aaron-56]. From this fairly remote start from the perspective of digital computers, there has been a gradually increasing use of computers in the analysis, evaluation, testing, and optimization of electric and electronic circuits and systems [Aaron-56].

From the early 1950's, engineers and researchers on circuit and systems have always been interested in the theoretical problems of CAD circuit analysis, optimization, and automated design. In many cases, results from applied physics and mathematics have been identified and used to advantage. At many locations around the world, in both industrial and academic environments, circuit and system researchers have been working extensively on new advances on CAD and have contributed significantly with outstanding results being documented in many scientific publications.

Modern CAD optimization techniques can now utilize most types of models, including multidimensional physical models. Space mapping (SM) [Bandler-94], [Koziel-08], offers a particularly powerful means of linking multidimensional numerical simulations (both physics-based and electromagnetic (EM) simulations) to CAD applications.

Trends for the future show that flexible macromodeling of devices and components will be created through SM models to replace central processing unit (CPU) intensive EM models [Snel-01]; and develop a design environment to work on large mixed-signal systems with the utilization of the Internet to incorporate manufacturing process requirements.

Furthermore, optimization software engines are appearing for wireless and microwave circuit design, which exploit both full-wave EM simulators and fast, empirical, coarse or surrogate models. It can be expected that commercial implementations of optimization-ready EM simulators incorporating exact or adjoint sensitivities [Alessandri-93], [Chung-00], [Ureel-96] will appear in the next decade, as well as robust algorithms for EM optimization fully exploiting SM and surrogate models. Similarly, knowledge-based artificial neural networks (ANN) techniques

[Rayas-Sánchez-04] are expected to play a significant role in future CAD.

The search for accurate models of active devices and passive components continues to be an imperative task. Advanced CAD technologies, such as SM and surrogate modeling, offer promising methodologies to address some of these challenges.

In the area of silicon validation, CAD techniques provide a means for designers to validate the design before physical implementation. Compared to traditional post-silicon validation, simulations (behavioral simulation) are much cheaper and faster to run. However, simulation results can deviate from the post-silicon measurements to some extent, due to inaccuracies of device models (components, channels, interconnects, etc.) and simplifications in behavioral models (e.g., in silicon transmitter and receiver circuits). Given such gaps between simulation and post-silicon validation measurements, there is an interest in how to use simulation to help post-silicon validation, and how post-silicon validation results can be used to calibrate pre-silicon CAD models. In addition to the inaccuracies in simulation, special techniques might be needed to integrate them with other post-silicon measurements considering industrial variations (i.e. silicon manufacturing process, voltage, temperature).

Nowadays, technologies such as formal verification, simulation acceleration and FPGA-based emulation allow covering much larger portions of the validation plans than traditional validation based on regular simulation. However, to really approach the overall verification and validation challenge holistically, a more unified verification infrastructure is needed to carry on from pre-silicon to post-silicon, but unfortunately this is where current methodology often breaks apart. In order to transform the post-silicon validation from an engineering art, practiced by few experienced engineers, to a technical discipline with solid foundations and systematic methodologies, new approaches and CAD techniques are required. Some approaches may include reliable system design, embedded systems, software test and verification, and simulation in post-silicon by using concepts like SM.

In 1965, Gordon Moore, Intel's cofounder, predicted that the number of transistors integrated per square inch on a die would double every year [Moore-65]. In subsequent years, the pace slowed, but the number of transistors has continued to double approximately every 18 months for the past three decades. Most experts expect that Moore's law will hold for at least two more decades. Die size will continue to grow larger, but, at the same time, minimum feature size will continue to shrink. As the manufacturing technology continues to advance, precise control of the

silicon process is becoming more challenging. As microprocessor design moves into the nanometer age and in order to keep up with Moore's law, many new nanotechnologies and circuit design techniques must be developed and adopted, all of which pose new test challenges that must be addressed concurrently. Otherwise, the cost of test would eventually surpass the cost of silicon manufacturing.

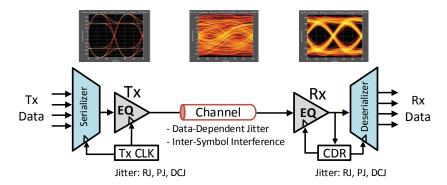

Undesired effects such as jitter, inter-symbol interference (ISI), crosstalk and others, can create multiple problems on the signal integrity of high-speed I/O's (HSIO) circuits, making maximum bus speeds difficult to achieve in practice. This problem is aggravated by the fact that channel speeds keep increasing from one generation bus technology to the next one. With each step upward to a higher speed and higher signaling frequencies, an HSIO circuit becomes more susceptible to distortions and anomalies which can effectively disrupt bus traffic and stall system throughput. In general, the higher the frequency of the signaling, the more susceptible the interconnect becomes to errors, re-transmissions and other anomalies. This is of particular concern for serial I/O's interfaces, such as Peripheral Component Interconnect Express (PCIe), Serial Advanced Technology Attachment (SATA), Universal Serial Bus (USB), and Ethernet interfaces.

During silicon validation, a failure (e.g., a too small eye diagram at the receiver) may be observed, or it may be concluded that the percentage of dies that may fail is too high for high volume production. In either situation, debugging is required. Ideally, the bug is root-caused, and fix it by re-designing. However, this approach is inefficient and costly. In practice, instead of re-designing the circuit, many link failures can be fixed by reconfiguring the I/O links through modifying the underlying training algorithm and/or by tuning knob settings.

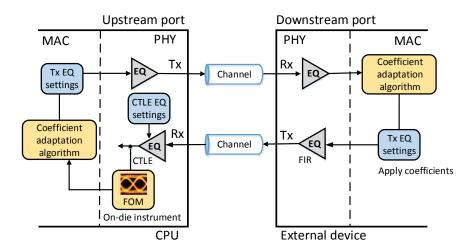

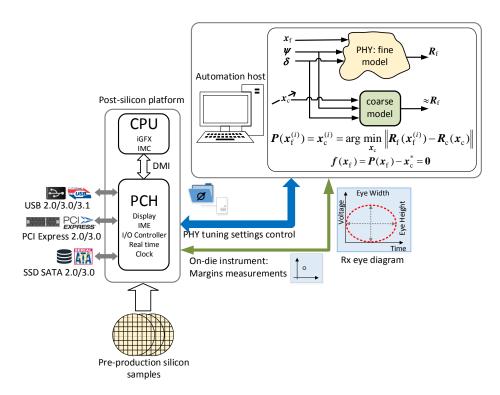

Training algorithms and physical layer (PHY) tuning are two important components in modern HSIO links. Training of a link is performed when the system boots, and it determines an optimal setting of sampling point (time and voltage) as well as transmitter (Tx)/receiver (Rx) coefficients, such as equalization (EQ) coefficients. This is usually an empirical algorithm given by expert knowledge of how the eye diagram is shaped. Obviously, the training algorithm has a very significant impact on eye margins, and is critical for I/O links to work properly.

PHY tuning is another important feature in mixed-signal systems. PHY tuning knobs are usually embedded in the I/O links, and can be digitally tuned to appropriate values. With transistor size keeping shrinking, there can be large die-to-die process variations. Besides, depending on the operating conditions (such as voltage supply and temperature), board impedance, different channel

loss, different add-in cards/DIMMs, the performance of I/O links can exhibit large variation. The PHY tuning provide a way to reconfigure I/O links in post-silicon to cancel out various fluctuations. Therefore, failures observed under one PHY tuning knob configuration might disappear under another knob configuration. However, it is usually unknown in pre-silicon which configuration gives the overall best performance. In other words, it is post-silicon validation's responsibility to search for "optimal" PHY tuning knob configurations that results in a good performance across all operating conditions. In the worst case, this means sweeping all possible combinations of all PHY tuning knobs – nearly prohibitive in the post-silicon validation time frame [Gu-12]. Therefore, CAD research directions are needed for reducing validation time/cost and improving validation accuracy/confidence [Keshava-10].

Within the computer server segment, there are conditions that further increase system complexities. These include nonflexible form factors, which implies that the channel physical designs remain unchanged. Therefore, PHY tuning based on EQ techniques are used to cancel any undesired effect [Rangel-Patiño-16]. The current industrial practices to perform PHY tuning consist of an exhaustive enumeration method, turning them into the most time-consuming processes in post-silicon validation [Rangel-Patiño-17b].

This doctoral dissertation presents several optimization techniques based on novel objective functions to optimize the Tx and Rx equalizers in a server post-silicon validation platform. This doctoral dissertation is organized as follows.

In Chapter 1, a description of post-silicon validation is provided; the convergence between post-silicon and pre-silicon is discussed along with key challenges in post-silicon HSIO validation. Some opportunities to overcome the current post-silicon challenges are discussed and potential solutions to improve efficiency and quality of HSIO validation are proposed.

Chapter 2 makes a review of basic concepts on equalization, as well as a review of some of the most popular Tx and Rx equalizer topologies in HSIO links is realized. The ISI phenomenon and its impact on HISO links is explained, and the concept of equalization is outlined.

Chapter 3 is devoted to HSIO links testing, at both chip and system levels, by using a design-for-testability (DFT) approach for the emerging equalization and compensation circuits used in modern I/O links, known as system marginality validation (SMV).

In Chapter 4, a holistic optimization approach is described, that merges system margining and jitter tolerance measurements to optimize the Rx analog circuitry during industrial post-silicon

validation. The methodology concurrently optimizes Rx system margins and jitter tolerance (JTOL), by defining an objective function that combines both type of measurements, and by using a Kriging surrogate-based modeling approach to efficiently perform optimization.

In Chapter 5, an efficient optimization methodology is proposed to find out the optimal coefficients for a reconfigurable finite impulse response (FIR) filter used for the Tx of an Ethernet interface. The procedure implies developing an effective objective function and by using direct numerical optimization in a post-silicon validation platform.

In Chapter 6, a new optimization methodology is proposed to find out the optimal subset of coefficients for the Tx and Rx in a PCIe equalization process. The procedure implies defining an effective objective function, and then applying a direct numerical optimization method using lab measurements in a post-silicon validation platform. To overcome the problem of multiple local minima in the measurement-based objective function, an efficient combination of pattern search and Nelder-Mead methods is employed.

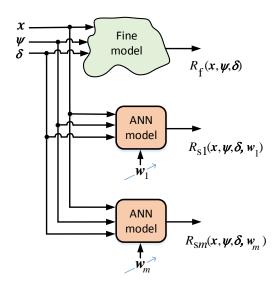

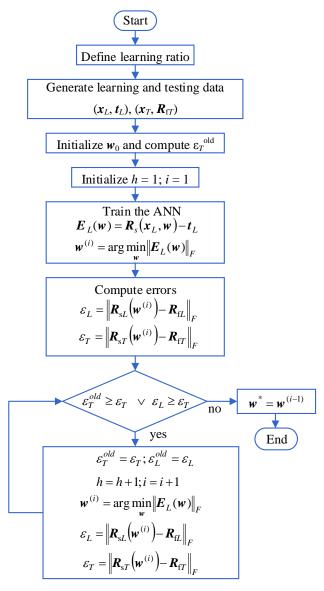

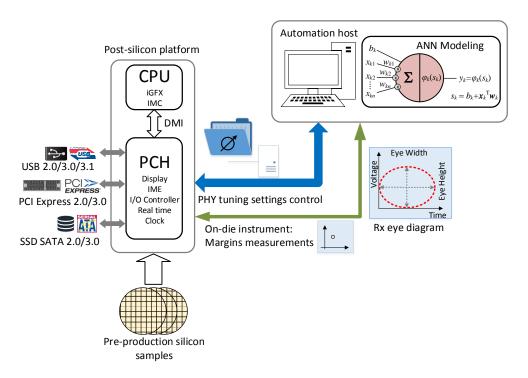

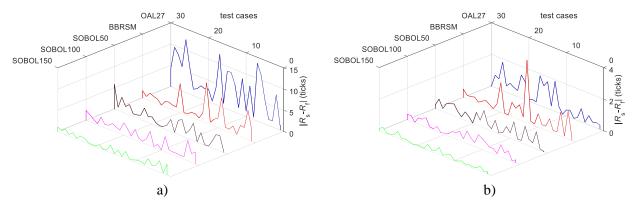

In Chapter 7, coarse surrogate models of an HSIO link are developed based on actual measurements of a server post-silicon validation platform. Several surrogate modeling techniques combined with different design of experiments (DoE) approaches are compared to find the best coarse model. A metamodeling approach is also proposed, based on ANN, to efficiently simulate the silicon equalizer Rx circuitry. The model is generated by using a frugal set of training data exploiting several DoE approaches to reduce the number of test cases.

In Chapter 8, the Broyden-based input space mapping algorithm is exploited to efficiently optimize the PHY tuning Rx equalizer settings for an HSIO interface. A good-enough surrogate model is used as the coarse model, and a post-silicon validation physical platform as the fine model. A map between the coarse and the fine model Rx equalizer settings is built, yielding an accelerated SM-based optimization of the PHY tuning process.

In the General Conclusions, the most relevant remarks about this doctoral dissertation are summarized, discussing the overall results of the proposed optimization techniques and the novel objective functions to optimize the Tx and Rx equalizers in a server validation platform. Some opportunities for future research are briefly outlined.

Finally, Appendix A shows the reference list of the thirteen internal research reports developed during the doctoral studies, and Appendix B shows the list of papers published during this same period of time.

There is an increasingly higher number of analog/mixed signal circuits in microprocessors and in Systems on Chip (SoC). A significant portion of those mixed-signal circuits are HSIO links. Improvements in signaling methods, circuits and process technology have allowed HSIO data rates to scale beyond 10 Gb/s over several legacy channels. It is evident that challenges of post-silicon validation are continuously increasing, along with a big pressure of maintaining aggressive launch schedules. With all these elements, post-silicon validation of HSIO links is hard and time-consuming, and can be critical for making a product release qualification decision. Therefore, in order to overcome these challenges, new post-silicon approaches are required. In this chapter, a description of post-silicon validation is provided; the convergence between post-silicon and presilicon is discussed along with key challenges in post-silicon HSIO validation. Some opportunities to overcome the current post-silicon challenges are discussed and potential solutions to improve efficiency and quality of HSIO validation are proposed.

## 1.1. Introduction

Complexity of new embedded systems has grown to an amazing level. Today's most advanced processors and SoC incorporate millions of transistors, and must be compatible with dozens of operating systems, hundreds of platform components and thousands of hardware devices and software applications. To ensure leading performance, reliability and compatibility in this complex environment, companies like Intel invests over hundreds of millions of dollars annually in component and platform validation [INTEL-03].

This internal processor complexity creates a huge number of possible test sequences, and this complexity is just one parameter to assess the validation challenges. Each component will be used in an enormous variety of platform configurations, and it will have to interoperate with many different motherboards, components, peripherals, operating systems and applications. It will also face various extremes of temperature, voltage and clock frequency. This variability of configurations and operating environments increases extremely the number of tests.

The combined effects of increased product complexity, performance requirements and

time-to-market (TTM) commitments have added tremendous pressure on validation, which is usually the last step prior to volume manufacturing. This challenges the validation teams to continuously assess their methods and processes, and look for opportunities to make validation faster and cheaper [Keshava-10].

The interfaces coming out from the new microprocessors, SoC and chipsets are now a lot faster, and there are many more of them. Additionally, the increase in the number of cores and threads and the inclusion of advanced power management and virtualization drive additional complexity, as well as new boundary conditions and bus requirements. Therefore, post-silicon validation is undertaking fundamental transformations, from radically changing environmental conditions [Keshava-09], [Patra-07], [Tiruvallur-09].

Post-silicon validation of a microprocessor is performed at various so called disciplines, including System Validation (SV), Compatibility Validation (CV), and Electrical Validation (EV) [INTEL-03], [Keshava-10], [Shkolnitsky-10]. Different types of validation focus on different specifications and execute in parallel. Finally, the post-silicon validation purpose is to qualify a product over all process corners and operating conditions. At the end of post-silicon validation process, a Product Release Qualification (PRQ) decision is made based on the validation results according to the risk assessment of how many systems may fail specifications.

Among post-silicon validation disciplines, EV focuses on validating electrical parameters/behaviors, including those of I/O links, phase-locked loop (PLLs), power grid, clock network, analog/mixed-signal circuits, training algorithms optimization and PHY tuning knob settings. As an increasing number of HSIO interfaces are integrated on die, a large portion of EV is devoted to the validation of HSIO to include PCIe, SATA, USB and Ethernet interfaces.

The goal of post-silicon EV I/O validation is to predict from a small set of experiments, the distribution of HSIO performances in high volume and under various operating conditions. This goal itself poses the greatest challenge for I/O validation since in practice only a limited number of experiments is finished within the post-silicon validation time-frame. On top of that, complexity in EV is aggravated by the need to compensate for circuit non-idealities to reach the increasing speeds. These non-idealities include: process variability, noise, non-linear circuit behavior, the need to accommodate other components, etc. This complexity translates to increased compensation and adaptation loops. These circuits require Design-For-x (DFx) and programmability which need to be validated in the context of the entire usage space. In addition, with SoC, many components

and power management solutions are added that create uncertainty on the die and on the platform. To overcome these problems, some areas of improvement have been identified [Gu-12]:

- a) Develop coverage metrics for I/O validation.

- b) Develop specialized data mining and analysis techniques to discover correlations among various sources of data, which can be used to increase validation efficiency.

- c) Maximize the usage of simulation and bridge the gap between simulation and validation results.

In this chapter, some key challenges in post-silicon validation of high-speed I/O links are presented and potential solutions to improve efficiency and quality of HSIO validation are reviewed.

## 1.2. Silicon Validation

The complexities of modern microprocessors have turned the validation of these components into an enormous task [Wile-05]. Silicon validation involves tens or hundreds of person-years and requires the computing power of large number of workstations. But even with all this effort, it is practically impossible to detect and fix all silicon bugs in the design before it tapes-out. Actually, statistics show that almost 50% of chips may require additional unplanned tape-outs because of functional bugs. Moreover, project plans may call for several planned tape-outs changes at intermediate stages before the final release of the silicon [Adir-11].

### 1.2.1 Pre-Silicon and Post-Silicon

Silicon validation techniques may be generally classified as pre-silicon and post-silicon. Pre-silicon validation refers to all of the validation activities performed before the first silicon is available. During the pre-silicon stage, the devices are tested in a virtual environment with complex simulation, emulation, and formal verification tools. However, the testing is done at the circuit level, not extending to the system-level. Therefore, after the first silicon is ready, post-silicon validation is done in a system environment looking for bugs missed in pre-silicon validation [Rotithor-00]. Post-silicon validation has been used for many years, and it can be attributed with the findings of many silicon bugs that escaped from pre-silicon validation. However, in general,

functional verification methodology for pre-silicon is still more mature than for post-silicon. Very few publications on post-silicon verification methodologies are available, and most research has centered on on-line checking and debugging capabilities of the validation platforms [Abramovici-06], [Chen-08], [Chang-07], [De Paula-08], [Wagner-08].

The objective of post-silicon validation is to ensure that the silicon design works properly under actual operating conditions while executing actual software, identifying and fixing bugs that may have been missed during pre-silicon validation. Therefore, post-silicon validation involves operating hundreds of manufactured silicon samples in actual customer application environments to validate a correct behavior over specified operating conditions. Due to the complexities of modern microprocessors, post-silicon validation is becoming significantly difficult and prohibitively expensive because existing techniques cannot manage with the total complexity of those systems [Abramovici-06], [Patra-07], [Yerramilli-06]. Post-silicon validation involves four major steps [Mitra-10]:

- a) Detecting a problem by running a stress environmental test sequence to end-user applications.

- b) Isolating the problem to a small region from the system failure.

- c) Identifying the root cause of the problem.

- d) Fixing or patching the problem, circuit editing or, as a last option, re-design.

Post-silicon validation has significant overlap with pre-silicon validation and high volume manufacturing (HVM) testing. Traditionally, most design bugs are detected during pre-silicon validation, and manufacturing defects are targeted by HVM testing. While both HVM testing and pre-silicon validation continue to be critical, post-silicon validation is becoming extremely important because of several unique aspects [Mitra-10]:

- a) Silicon health cannot just rely on pre-silicon validation to detect all design bugs. Circuit simulation is several orders of magnitude slower than actual silicon and then unacceptable under the new TTM challenges.

- b) A silicon part will see more events in its first few minutes of power-up than it has in its entire prior existence in simulation and emulation.

- c) Modern microprocessor designs are so large and complex that it is virtually impossible for any individual to know every aspect of the design, or even of a large circuit block.

- d) Several interactions between a design and the electrical state of a system are becoming

significant, e.g., signal integrity (cross-talk and power-supply noise), thermal effects, and process variations. Such interactions can result in incorrect behavior (electrical bugs). Accurate modeling of all these electrical phenomenon is usually very difficult during presilicon validation.

- e) It may be very difficult to create accurate and effective fault models for bugs may be caused by subtle interactions between a design and physical effects (electrical bugs) or by design errors (logic bugs).

- f) Unlike manufacturing testing, where the primary objective is to detect defects, post-silicon validation involves localizing, root causing and fixing bugs. Bug localization generally dominates post-silicon validation effort and costs [Josephson-06]. Moreover, unlike defect diagnosis which targets manufacturing yield improvement, the presence of one or more bugs may prevent detection of errors caused by other bugs. Such bugs are also referred to as blocking bugs because they may slow down the design or validation cycle [Anis-08], [Keshava-10].

## 1.2.2 Post-Silicon Validation Disciplines

As mentioned before, the disciplines of post-silicon validation include SV, CV, and EV [Bentley-01], [INTEL-03]. SV is typically performed on custom validation boards using specially written tests. These boards are usually larger than commercial boards because they provide room for additional connections to probing, measurement, and debug tools, and allow interchangeability of components. The tests run the range of operating system (OS) level programs and random instruction tests, down to hardware-coded patterns and built-in self-tests. The tool sets involved in SV are quite different from that in the pre-silicon world and rely heavily on in-target probes, logic analyzers, hardware accelerators, and tools using system management interrupts to bound the problem and reproduce it in a simulation environment [Silas-03]. Tests include focused tests to stress one aspect of the die, random instruction tests, or even OS-level applications. In CV, silicon is tested using commercially available operating systems and applications with a focus on ensuring backward compatibility with existing software, and running additional tests in an environment more resembling the end user's own platform and applications. EV focuses on validating the part from an electrical perspective, analyzing its inherent performance and margin, and on its electrical

### 1. POST-SILICON VALIDATION

interaction with other components on the board. Tests here range from commercial applications, to specific patterns that stress the various components and platform interconnections. Speed-paths are usually confronted by a separate step in the overall validation, using both platform and high-speed testers [Gray-08]. While testers provide very good controllability of the voltage and temperature environment, they may not duplicate the environment of a real system and may produce optimistic results. Platform-level tests enable to reproduce this environment better, and even provide patterns for future high-volume tests [Keshava-10].

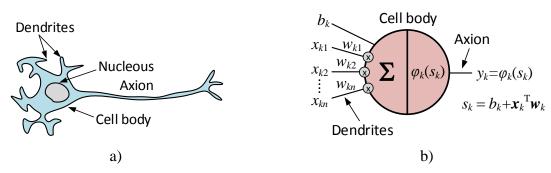

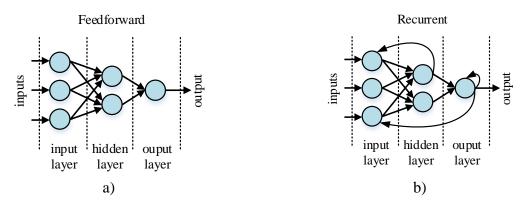

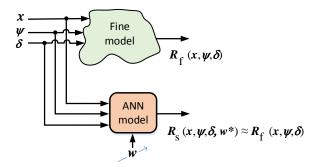

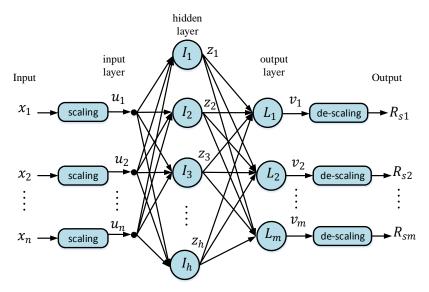

### 1.2.3 Post-Silicon Electrical Validation