# INSTITUTO TECNOLÓGICO Y DE ESTUDIOS SUPERIORES DE OCCIDENTE

Reconocimiento de validez oficial de estudios de nivel superior según acuerdo secretarial 15018, publicado en el Diario Oficial de la Federación el 29 de noviembre de 1976.

Departamento de Electrónica, Sistemas e Informática

DOCTORADO EN CIENCIAS DE LA INGENIERÍA

# TÉCNICAS DE APRENDIZAJE AUTOMÁTICO Y ENFOQUES DE OPTIMIZACIÓN PARA VALIDACIÓN Y PRUEBAS ANALÓGICAS

Tesis que para obtener el grado de Doctor en Ciencias de la Ingeniería

presenta: Andrés Viveros Wacher

Director de tesis: Dr. José Ernesto Rayas Sánchez

Tlaquepaque, Jalisco. Diciembre de 2020

TÍTULO: Técnicas de aprendizaje automático y enfoques de

optimización para validación y pruebas analógicas

**AUTOR:** Andrés Viveros Wacher

Ingeniero Eléctrico Electrónico (Universidad Nacional

Autónoma de México, México)

Maestro en Ingeniería de Sistemas Microelectrónicos

(Universidad de Bristol, Reino Unido)

**DIRECTOR DE TESIS:** José Ernesto Rayas Sánchez

Profesor Numerario del Departamento de Electrónica, Sistemas

e Informática, ITESO

Ingeniero en Electrónica (ITESO, México)

Maestro en Sistemas Electrónicos (ITESM Campus Monterrey,

México)

Doctor en Ingeniería Eléctrica (Universidad McMaster,

Canadá)

Senior, IEEE

**NÚMERO DE PÁGINAS:** xxxii, 141

## ITESO - The Jesuit University of Guadalajara

Department of Electronics, Systems, and Informatics

DOCTORAL PROGRAM IN ENGINEERING SCIENCES

# MACHINE LEARNING TECHNIQUES AND OPTIMIZATION APPROACHES FOR ANALOG VALIDATION AND TESTING

Thesis to obtain the degree of DOCTOR IN ENGINEERING SCIENCES

Presents: Andrés Viveros-Wacher

Thesis Director: Dr. José Ernesto Rayas-Sánchez

Tlaquepaque, Jalisco, México December 2020 TITLE: Machine Learning Techniques and Optimization

**Approaches for Analog Validation and Testing**

**AUTHOR:** Andrés Viveros-Wacher

Bachelor's degree in electrical and electronics engineering

(Universidad Nacional Autónoma de México, Mexico)

Master's degree in microelectronics systems engineering

(University of Bristol, UK)

**THESIS DIRECTOR:** José Ernesto Rayas-Sánchez

Department of Electronics, Systems, and Informatics, ITESO-

The Jesuit University of Guadalajara

Bachelor's degree in electronics engineering (ITESO, Mexico)

Master's degree in electrical engineering (ITESM, Mexico)

Ph.D. degree in electrical engineering (McMaster University,

Canada)

Senior, IEEE

**NUMBER OF PAGES:** xxxii, 141

# To my wife, Pamela, whose support and encouragement have made this achievement possible

#### Resumen

La validación y pruebas analógicas post-silicio de enlaces de entrada/salida (HSIO, por sus siglas en inglés) en plataformas de computadora de alto rendimiento tienen retos continuamente crecientes por varios factores: la ley de Moore sigue avanzando con una constante miniaturización de los nodos tecnológicos, la complejidad de los productos continúa creciendo junto con funcionalidades más demandantes, y las velocidades de datos continúan aumentando con las nuevas generaciones de interfaces HSIO, entre otros. Por otro lado, existe la necesidad de mantener calendarios agresivos de lanzamiento de productos para mantener competitividad en el mercado. En este escenario, es crucial para las compañías encontrar soluciones innovadoras para acelerar los procesos de validación y prueba sin sacrificar la calidad de los resultados. Esta tesis doctoral propone una serie de metodologías de aprendizaje automático y de optimización para mejorar varios procesos de validación y pruebas analógicas, en su mayoría asociadas a enlaces HSIO en plataformas de cómputo modernas. Primero demuestra cómo los márgenes del diagrama de ojo del receptor son significativamente mejorados al usar un enfoque de optimización basado en diseño de experimentos. Posteriormente, muestra cómo la prueba de tolerancia a fluctuaciones en el tiempo es dramáticamente acelerada al ejecutar un algoritmo eficiente de optimización numérica. La presente tesis también describe cómo algoritmos de aprendizaje automático se usan para crear modelos sustitutos del sistema bajo prueba, para acelerar el proceso de sintonización de una plataforma física durante la validación eléctrica post-silicio usando optimización basada en sustitutos y mapeo espacial agresivo. Adicionalmente, la tesis elabora sobre la identificación automática de fallas analógicas, desarrollando modelos de redes neuronales de inyección de fallas y un algoritmo de detección basado en optimización explotando la extracción de parámetros restringida. Finalmente, esta tesis doctoral describe cómo se pueden entrenar modelos de redes neuronales profundas para clasificar la precisión de la extrapolación de la tasa de errores de bits (BER, por sus siglas en inglés) en mediciones de márgenes para estándares industriales de BER. Cada metodología propuesta es validada con casos de prueba, demostrando no solo la eficiencia de las técnicas propuestas sino también mejoras significativas a los procesos analógicos postsilicio en general. Algunas oportunidades de investigación futura y desarrollos con potencial promisorio asociados a las pruebas y validación analógica post-silicio también son identificados.

### **Summary**

Analog post-silicon validation and testing of high-speed input/output (HSIO) links in highperformance computer platforms has ever-increasing challenges caused by several factors: Moore's law continues to advance with constant technology node miniaturization, product complexity keeps increasing along with more demanding functionalities, and data rates continue to escalate with new generations of HSIO interfaces, among others. On the other hand, there is a need to maintain aggressive product launch schedules in order to maintain market competitiveness. This scenario makes crucial for companies to find innovative solutions to accelerate validation and testing processes without sacrificing results quality. This doctoral dissertation proposes a set of machine learning and optimization methodologies aimed at improving several analog validation and testing industrial processes, most of them associated to HSIO links in modern computer platforms. It first demonstrates how receiver eye diagram margins are significantly improved by using an optimization approach based on design of experiments. It subsequently shows how the jitter tolerance test is dramatically accelerated by employing an efficient numerical optimization algorithm during execution. The present Ph.D. thesis also describes how machine learning algorithms are exploited to create surrogate models of the system under test to accelerate the physical platform tuning process during electrical post-silicon validation by using surrogate-based optimization and aggressive space mapping. Additionally, the proposed doctoral dissertation elaborates on automated analog fault identification, for which fault injection neural network models are developed by an optimization-based detection algorithm that exploits constrained parameter extraction. Finally, this Ph.D. thesis describes how deep neural network models can be properly trained to classify bit error rate (BER) extrapolation precision in margin measurements under specified BER industry standards. Each methodology proposed in this doctoral dissertation is properly validated by suitable test cases, demonstrating not only the efficiency of the proposed techniques but also the improvements to the overall analog post-silicon processes. Some future research opportunities and promising potential developments associated to analog post-silicon validation and testing are also envisioned.

## Acknowledgements

The author wishes to express his sincere appreciation to Dr. José Ernesto Rayas-Sánchez, professor of the Department of Electronics, Systems, and Informatics at ITESO, and director of research in the Computer-Aided Engineering of Circuits and Systems (CAECAS) group at ITESO, for his encouragement, expert guidance, and keen supervision as doctoral dissertation director throughout the course of this work. The author offers his gratitude to Dr. Adam Norman from Intel Corporation, for his support during the development of this dissertation. He also thanks Dr. Paulo López-Meyer, Dr. Omar Longoria-Gándara, Dr. José Luis Pizano-Escalante, and Dr. Zabdiel Brito-Brito, members of his Ph.D. Thesis Examination Committee, for their interest, assessment, and suggestions.

Special thanks are due to Dr. Zabdiel Brito-Brito, from CAECAS research group at ITESO. It is the author's pleasure to acknowledge fruitful collaboration and stimulating discussions with his colleagues of CAECAS research group at ITESO — The Jesuit University of Guadalajara: Francisco Rangel-Patiño, José Luis Chávez-Hurtado, Rafael del-Rey-Acuña, Felipe de Jesús Leal-Romo, Jorge Dávalos-Guzmán, Rosa Jaqueline Sánchez-Mesa, Roberto Loera-Díaz and Edna Moreno-Mojica.

The author also thanks his peers and colleagues from Intel Corporation, for fruitful cooperation and helpful technical discussions: Ricardo Baca-Baylón, Edgar A. Vega-Ochoa, Miguel Dávalos-Santana, Jesús Gómez-Lopez, Alejandro Moscoso, Suriyaprakash Natarajan, Prashant Goteti, and many others.

The author gratefully acknowledges the financial assistance through a scholarship granted by the *Consejo Nacional de Ciencia y Tecnología* (CONACYT), Mexican Government, as well as the financial support provided by Intel Corporation.

Finally, special thanks are due to my family: my wife Pamela, my parents, and my sister, for their understanding, patience, and continuous loving support.

# Contenido

| Resum   | en                                                                      | vii  |

|---------|-------------------------------------------------------------------------|------|

| Summa   | <i>rry</i>                                                              | ix   |

| Recono  | ocimientos                                                              | xi   |

| Conten  | ido                                                                     | xiii |

| Conten  | ts                                                                      | xix  |

| Lista d | e figuras                                                               | XXV  |

| Lista d | e tablas                                                                | xxix |

| Lista d | e acrónimos                                                             | xxxi |

| Introdu | ıcción                                                                  | 1    |

| 1. Técn | icas de optimización para acelerar la validación analógica              | 5    |

| 1.1.    | DISEÑO DE EXPERIMENTOS                                                  | 7    |

|         | 1.1.1 Diseño factorial                                                  | 7    |

|         | 1.1.2 Diseño factorial fraccionado                                      | 8    |

|         | 1.1.3 Metodología de superficie de respuesta y diseño central compuesto | 9    |

|         | 1.1.4 Método de ascenso más pronunciado                                 | 10   |

|         | 1.1.5 Diseño central compuesto                                          | 10   |

| 1.2.    | DIAGRAMAS DE OJO EN ENLACES HSIO                                        | 11   |

| 1.3.    | Técnicas de ecualización                                                | 12   |

|         | 1.3.1 Ecualización del transmisor                                       | 12   |

|         | 1.3.2 Ecualización del receptor                                         | 12   |

| 1.4.    | Metodología de maximización del área del ojo del Rx                     | 13   |

| 1.5     | Resultados                                                              | 1.4  |

#### CONTENIDO

|    | 1.6.  | Validación post-silicio                                                           | 20 |

|----|-------|-----------------------------------------------------------------------------------|----|

|    | 1.7.  | Pruebas de tolerancia a fluctuaciones                                             | 21 |

|    | 1.8.  | Optimización de JTOL                                                              | 22 |

|    |       | 1.8.1 Búsqueda de la sección áurea                                                | 23 |

|    |       | 1.8.2 Búsqueda hacia abajo                                                        | 25 |

|    | 1.9.  | Casos de prueba                                                                   | 25 |

|    |       | 1.9.1 Caso de prueba 1: SATA3                                                     | 25 |

|    |       | 1.9.2 Caso de prueba 2: USB3                                                      | 27 |

|    | 1.9.  | Conclusiones                                                                      | 28 |

| 2. |       | lelado sustituto y optimizacióon de diseño de plataformas físiscas de rendimiento |    |

|    | 2.1.  | Descripción del sistema                                                           | 31 |

|    | 2.2.  | Diseño de experimentos (DoE)                                                      | 31 |

|    |       | 2.2.1 Box Behnken (BB)                                                            | 32 |

|    |       | 2.2.2 Arreglos ortogonales (OA)                                                   | 32 |

|    |       | 2.2.3 Sobol 33                                                                    |    |

|    | 2.3.  | Modelado sustituto y optimización                                                 | 33 |

|    |       | 2.3.1 Formulación del modelo sustituto                                            | 33 |

|    |       | 2.3.2 Técnicas de modelado sustituto                                              | 34 |

|    |       | 2.3.3 Optimización directa del modelo sustituto                                   | 35 |

|    | 2.4.  | Resultados y comparaciones                                                        | 36 |

|    | 2.5.  | Aprendizaje automático en validación post-silicio                                 | 39 |

|    | 2.6.  | Metamodelado del receptor basado en ANN                                           | 40 |

|    |       | 2.6.1 Topología de la ANN                                                         | 41 |

|    |       | 2.6.2 Modelado y entrenamiento de la ANN                                          | 41 |

|    | 2.7.  | Configuración experimental del sistema y enfoques de DoE                          | 43 |

|    | 2.8.  | Resultados del modelado neuronal                                                  | 44 |

|    | 2.9.  | Mapeo espacial a la entrada basado en Broyden                                     | 46 |

|    |       | 2.9.1 Modelo fino                                                                 | 47 |

|    |       | 2.9.2 Modelo burdo                                                                | 48 |

|    |       | 2.9.3 Función objetivo                                                            | 49 |

|    | 2.10. | Optimización ASM                                                                  | 49 |

|    | 2.11.                                                                       | Resultados  | s de la optimización                                             | 52 |  |  |  |

|----|-----------------------------------------------------------------------------|-------------|------------------------------------------------------------------|----|--|--|--|

|    | 2.12.                                                                       | Conclusion  | nes                                                              | 53 |  |  |  |

| 3. | Diagnóstico de fallas analógicas aprovechando redes neuronales artificiales |             |                                                                  |    |  |  |  |

|    | 3.1.                                                                        | Definición  | de fallas                                                        | 56 |  |  |  |

|    | 3.2.                                                                        | La importa  | ancia del diagnóstico de fallas                                  | 57 |  |  |  |

|    | 3.3.                                                                        | Fallas digi | tales vs analógicas                                              | 58 |  |  |  |

|    | 3.4.                                                                        | Modelado    | de fallas analógicas                                             | 59 |  |  |  |

|    |                                                                             | 3.4.1 Mod   | elos de fallas burdas                                            | 60 |  |  |  |

|    |                                                                             | 3.4.2 Mod   | elos de fallas paramétricas                                      | 61 |  |  |  |

|    | 3.5.                                                                        | Métodos d   | e diagnóstico de fallas basados en modelos                       | 61 |  |  |  |

|    |                                                                             | 3.5.1 Méto  | odos de diagnóstico de fallas determinísticos                    | 61 |  |  |  |

|    |                                                                             | 3.5.2 Méto  | odos de diagnóstico de fallas estocásticos                       | 62 |  |  |  |

|    |                                                                             | 3.5.3 Diag  | nóstico de fallas para eventos discretos y sistemas híbridos     | 62 |  |  |  |

|    |                                                                             | 3.5.3 Diag  | nóstico de fallas para sistemas en red y distribuidos            | 63 |  |  |  |

|    | 3.6.                                                                        | Métodos d   | e diagnóstico de fallas basados en señales                       | 63 |  |  |  |

|    | 3.7.                                                                        | Métodos b   | asados en conocimiento                                           | 64 |  |  |  |

|    |                                                                             | 3.7.1 Méto  | odos basados en sistemas expertos                                | 64 |  |  |  |

|    |                                                                             | 3.7.2 Anál  | lisis de tendencia cualitativo                                   | 65 |  |  |  |

|    |                                                                             | 3.7.3 Méto  | odos de diagnóstico de fallas basados en análisis estadístico    | 65 |  |  |  |

|    |                                                                             | 3.7.4 Méto  | odos de diagnóstico de fallas basados en análisis no estadístico | 66 |  |  |  |

|    |                                                                             | 3.7.5 Méto  | odos de diagnóstico de fallas dirigidos por datos conjuntos      | 66 |  |  |  |

|    | 3.8.                                                                        | Métodos h   | úbridos de diagnóstico de fallas                                 | 66 |  |  |  |

|    | 3.9.                                                                        | Diagnóstic  | eo activo de fallas                                              | 67 |  |  |  |

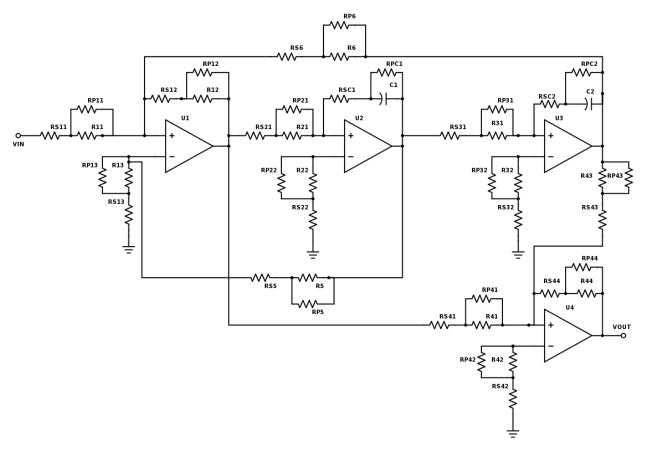

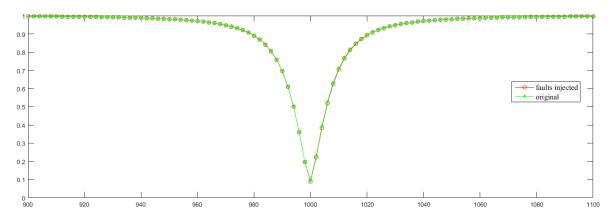

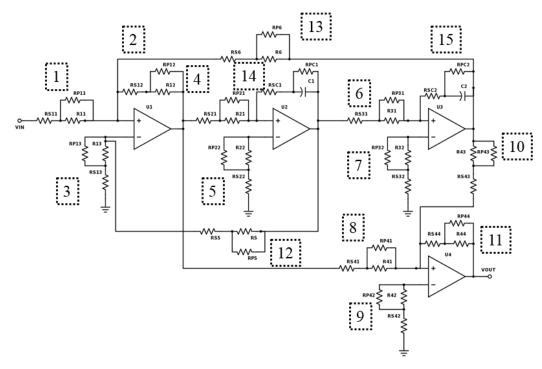

|    | 3.10.                                                                       | Introducci  | ón al modelado neuronal de fallas burdas analógicas              | 67 |  |  |  |

|    | 3.11.                                                                       | Modelos d   | e fallas analógicas                                              | 69 |  |  |  |

|    | 3.12.                                                                       | Modelado    | neuronal de fallas analógicas                                    | 70 |  |  |  |

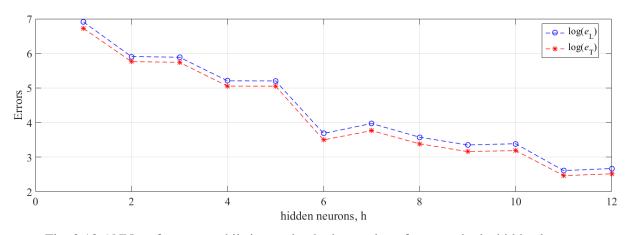

|    |                                                                             | 3.12.1      | Formulación del modelo neuronal                                  | 70 |  |  |  |

|    |                                                                             | 3.12.2      | Características y entrenamiento de la ANN                        | 71 |  |  |  |

|    |                                                                             | 3.12.3      | Identificación de fallas por extracción de parámetros            | 72 |  |  |  |

|    | 3.13.                                                                       | Ejemplo 1   | : Filtro rechaza banda de estado variable                        | 74 |  |  |  |

|    |                                                                             | 3.13.1      | Descripción del circuito                                         | 74 |  |  |  |

#### CONTENIDO

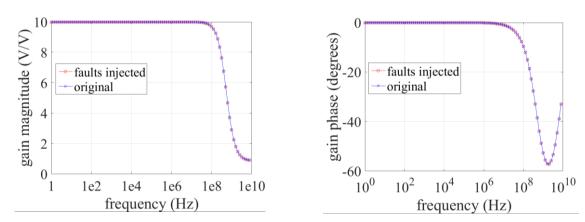

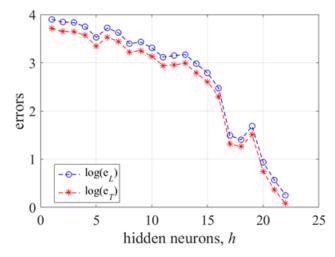

|    |          | 3.13.2         | Modelo neuronal de fallas y entrenamiento                      | 75         |

|----|----------|----------------|----------------------------------------------------------------|------------|

|    |          | 3.13.3         | Extracción de parámetros para la identificación de fallas      | 77         |

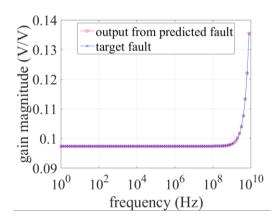

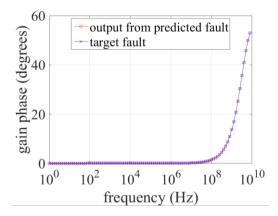

|    | 3.14.    | . Ejemplo 2: A | Amplificador de voltaje RF CMOS con retroalimentación negativa | 78         |

|    |          | 3.14.1         | Descripción del circuito                                       | 78         |

|    |          | 3.14.2         | Modelo neuronal de fallas y entrenamiento                      | 78         |

|    |          | 3.14.3         | Extracción de parámetros para la identificación de fallas      | 79         |

|    | 3.15.    | . Formulación  | generalizada del modelo neuronal                               | 80         |

|    | 3.16     | . Ejemplo 3: F | Filtro reconfigurable microcinta pasa banda                    | 81         |

|    |          | 3.16.1         | Descripción del circuito                                       | 82         |

|    |          | 3.16.2         | Modelo neuronal de fallas y entrenamiento                      | 82         |

|    |          | 3.16.3         | Extracción de parámetros para la identificación de fallas      | 84         |

|    | 3.17     | . Conclusione  | s                                                              | 84         |

|    | 3.7      |                |                                                                |            |

| 4. |          |                | onal profundo de la extrapolación del BER en enlaces           | 87         |

|    |          |                |                                                                |            |

|    | 4.1.     |                | de BER                                                         |            |

|    | 4.2.     |                | de medición en un ambiente industrial                          |            |

|    | 4.3.     |                | de datos sintéticos                                            |            |

|    | 4.4.     |                | del problema de modelado de la extrapolación del BER           |            |

|    | 4.5.     |                | ronales profundos                                              |            |

|    | 4.6.     | _              | propuesta de la DNN                                            |            |

|    | 4.7.     |                |                                                                |            |

|    | 4.8.     | Conclusione    | s                                                              | 98         |

| Ge | nera     | l Conclusion   | ns                                                             | 101        |

| •  |          |                |                                                                |            |

| Co | onclu    | siones gene    | rales                                                          | 105        |

| Aı | oéndi    | ce             |                                                                | 109        |

| -1 |          |                |                                                                |            |

|    | A.<br>B. | _              | ortes internos de investigaciónlicaciones                      |            |

|    | ъ.       | =              | los de revista                                                 |            |

|    |          |                | los de congresos                                               | 113<br>114 |

|    |          | D.Z. AHICH     | 105 UE COURTESUS                                               |            |

#### CONTENIDO

| Bibliografía       | 117 |

|--------------------|-----|

| Índice de autores  | 133 |

| Índice de términos |     |

# **Contents**

| Re  | sumo    | en                                                              | vii  |

|-----|---------|-----------------------------------------------------------------|------|

| Su  | mma     | ry                                                              | ix   |

| Ac  | knov    | vledgements                                                     | xi   |

| Co  | nten    | ido                                                             | xiii |

| Co  | nten    | ts                                                              | xix  |

| Lis | st of ] | Figures                                                         | XXV  |

| Lis | st of ' | Tables                                                          | xxix |

| Lis | st of . | Acronyms                                                        | xxxi |

| Int | trodu   | iction                                                          | 1    |

| 1.  | Opt     | imization Techniques to Accelerate Analog Validation            | 5    |

|     | 1.1.    | DESIGN OF EXPERIMENTS                                           | 7    |

|     |         | 1.1.1 Factorial Design                                          | 7    |

|     |         | 1.1.2 Fractional Factorial Design                               | 8    |

|     |         | 1.1.3 Response Surface Methodology and Central Composite Design | 9    |

|     |         | 1.1.4 Steepest Ascent Method                                    | 10   |

|     |         | 1.1.5 Central Composite Design                                  | 10   |

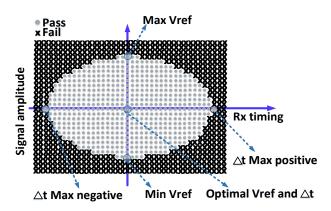

|     | 1.2.    | EYE DIAGRAMS IN HSIO LINKS                                      | 11   |

|     | 1.3.    | EQUALIZATION TECHNIQUES                                         | 12   |

|     |         | 1.3.1 Transmitter Equalization                                  | 12   |

|     |         | 1.3.2 Receiver Equalization                                     | 12   |

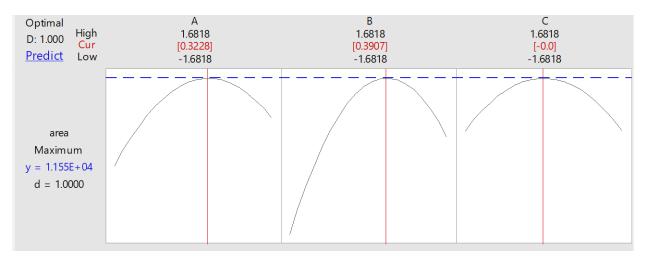

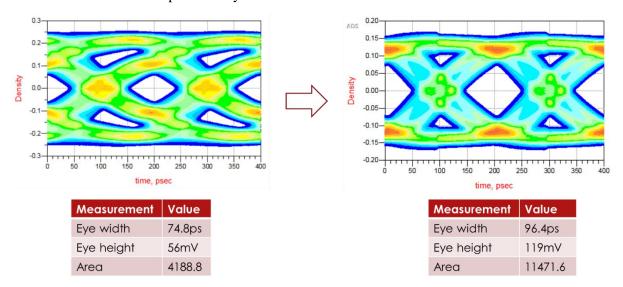

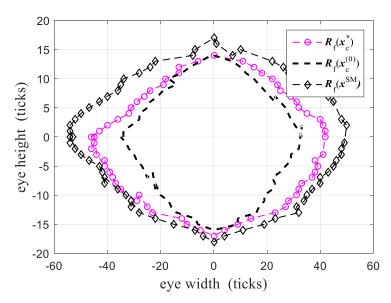

|     | 1.4.    | RX EYE AREA MAXIMIZATION METHODOLOGY                            | 13   |

|     | 1.5     | RESULTS                                                         | 14   |

#### **CONTENTS**

|    | 1.6.  | POST-SILICON VALIDATION                                                    | 20 |

|----|-------|----------------------------------------------------------------------------|----|

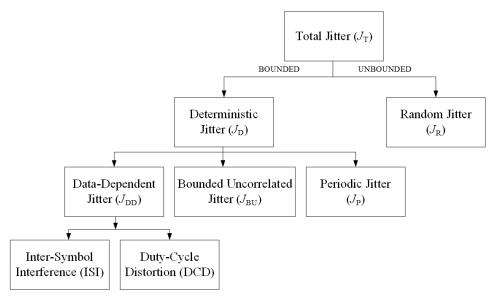

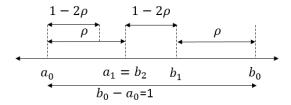

|    | 1.7.  | JITTER TOLERANCE TESTING                                                   | 21 |

|    | 1.8.  | JTOL OPTIMIZATION                                                          | 22 |

|    |       | 1.8.1 Golden Section Search                                                | 23 |

|    |       | 1.8.2 Downwards Search                                                     | 25 |

|    | 1.9.  | TEST CASES                                                                 | 25 |

|    |       | 1.9.1 Test Case 1: SATA3                                                   | 25 |

|    |       | 1.9.2 Test Case 2: USB3                                                    | 27 |

|    | 1.10. | Conclusions                                                                | 28 |

| 2. |       | rogate based Modeling and Design Optimization of High-Perf sical Platforms |    |

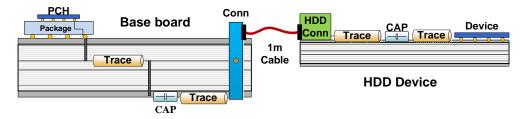

|    | 2.1.  | SYSTEM DESCRIPTION                                                         | 31 |

|    | 2.2.  | DESIGN OF EXPERIMENTS                                                      | 31 |

|    |       | 2.2.1 Box Behnken (BB)                                                     | 32 |

|    |       | 2.2.2 Orthogonal Arrays (OA)                                               | 32 |

|    |       | 2.2.3 Sobol 33                                                             |    |

|    | 2.3.  | SURROGATE MODELING AND OPTIMIZATION                                        | 33 |

|    |       | 2.3.1 Surrogate Model Formulation                                          | 33 |

|    |       | 2.3.2 Surrogate Modeling Techniques                                        | 34 |

|    |       | 2.3.3 Direct Surrogate Model Optimization                                  | 35 |

|    | 2.4.  | RESULTS AND COMPARISONS                                                    | 36 |

|    | 2.5.  | MACHINE LEARNING IN POST-SILICON VALIDATION                                | 39 |

|    | 2.6.  | ANN-BASED RECEIVER METAMODELING                                            | 40 |

|    |       | 2.6.1 ANN Topology                                                         | 41 |

|    |       | 2.6.2 ANN Modeling and Training                                            | 41 |

|    | 2.7.  | EXPERIMENTAL SYSTEM CONFIGURATION AND DOE APPROACHES                       | 43 |

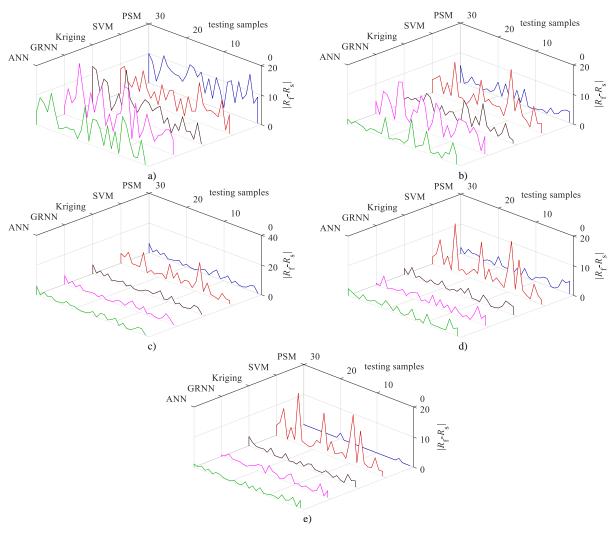

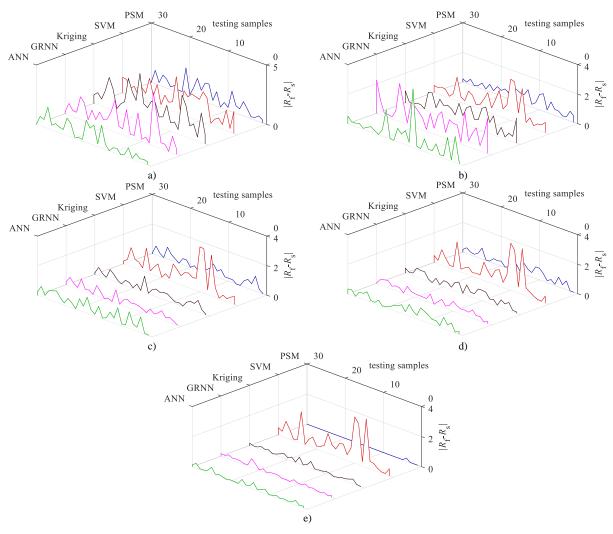

|    | 2.8.  | NEURAL MODELING RESULTS                                                    | 44 |

|    | 2.9.  | BROYDEN-BASED INPUT SPACE MAPPING                                          | 46 |

|    |       | 2.9.1 Fine Model                                                           | 47 |

|    |       | 2.9.2 Coarse Model                                                         | 48 |

|    |       | 2.9.3 Objective Function                                                   | 49 |

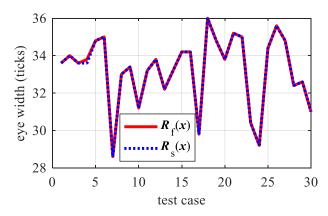

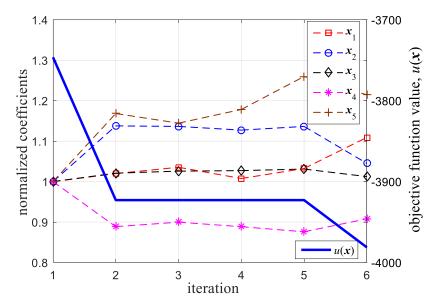

|    | 2 10  | ASM OPTIMIZATION                                                           | 49 |

|    | 2.11. | OPTIMIZATION OF THE PROPERTY O | ON RESULTS                                        | 52 |

|----|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------|----|

|    | 2.12  | . Conclusion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | NS                                                | 53 |

| 3. | Ana   | log Faults                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Diagnosis Exploiting Artificial Neural Networks   | 55 |

|    | 3.1.  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | OF FAULTS                                         |    |

|    | 3.2.  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | TANCE OF FAULT DIAGNOSIS                          |    |

|    | 3.3.  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Analog Faults                                     |    |

|    | 3.4.  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Analog Faults                                     |    |

|    |       | 3.4.1 Gross                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Fault Models                                      | 60 |

|    |       | 3.4.2 Param                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | netric Fault Models                               | 61 |

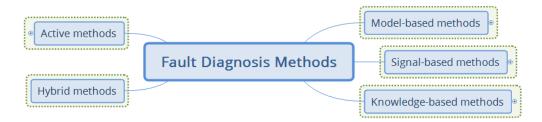

|    | 3.5.  | MODEL-BAS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | SED FAULT DIAGNOSIS METHODS                       | 61 |

|    |       | 3.5.1 Determ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | ministic Fault Diagnosis Methods                  | 61 |

|    |       | 3.5.2 Stocha                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | astic Fault Diagnosis Methods                     | 62 |

|    |       | 3.5.3 Fault 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Diagnosis for Discrete Events and Hybrid Systems  | 62 |

|    |       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Diagnosis for Networked and Distributed Systems   |    |

|    | 3.6.  | SIGNAL-BAS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | SED FAULT DIAGNOSIS METHODS                       | 63 |

|    | 3.7.  | KNOWLEDG                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | E-Based Methods                                   | 64 |

|    |       | 3.7.1 Exper                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | t-system-based Methods                            | 64 |

|    |       | 3.7.2 Qualit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | tative Trend Analysis                             | 65 |

|    |       | 3.7.3 Statist                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | tical-analysis-based Fault Diagnosis Methods      | 65 |

|    |       | 3.7.4 Non-s                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | tatistical-analysis-based Fault Diagnosis Methods | 66 |

|    |       | 3.7.5 Joint I                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Data-driven Fault Diagnosis Methods               | 66 |

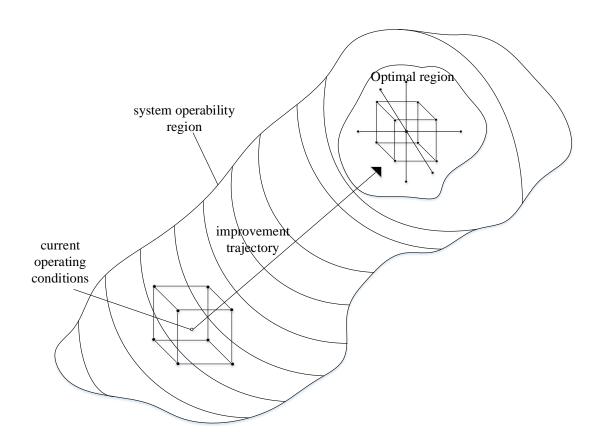

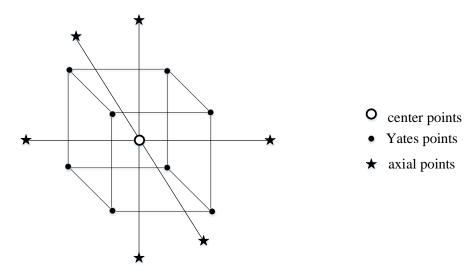

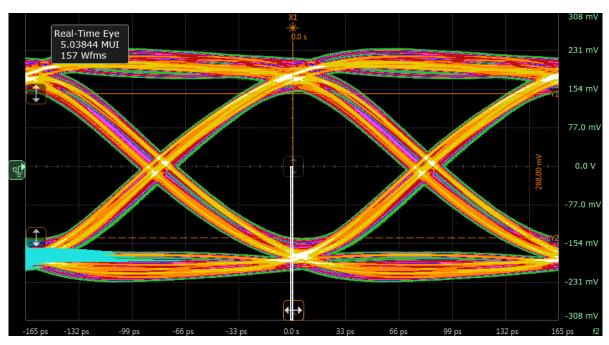

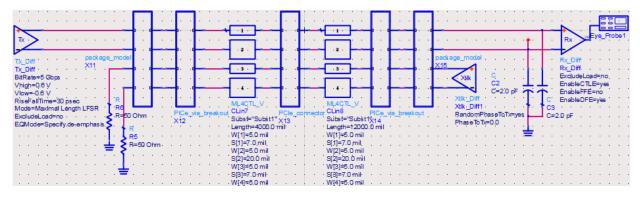

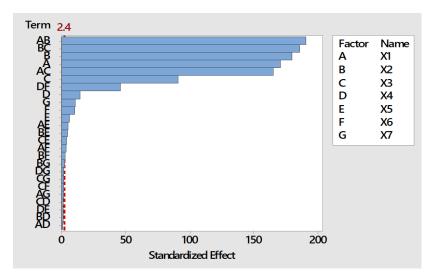

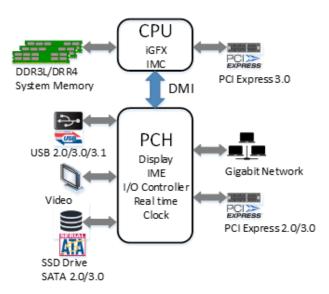

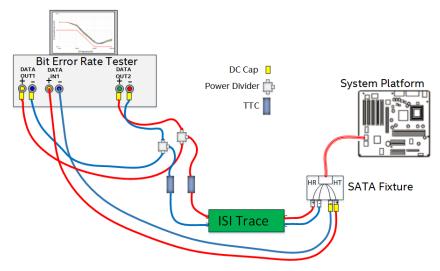

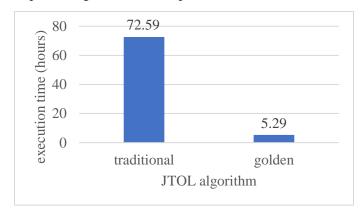

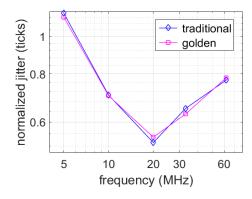

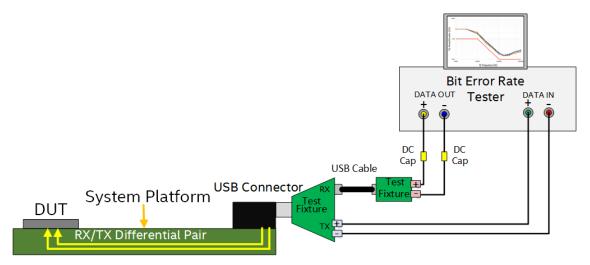

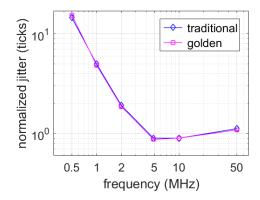

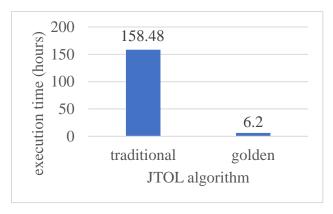

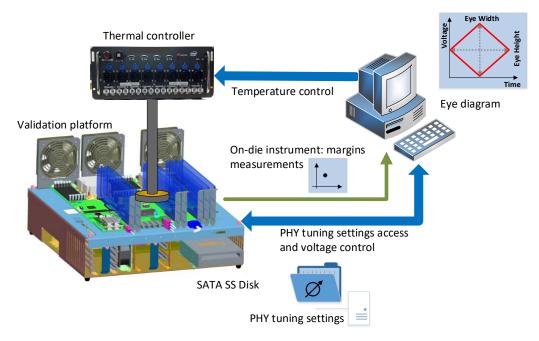

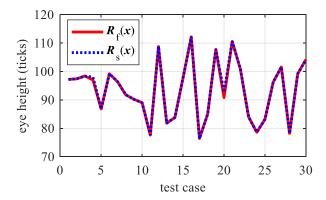

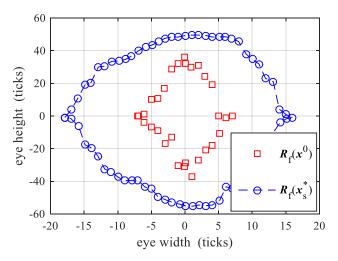

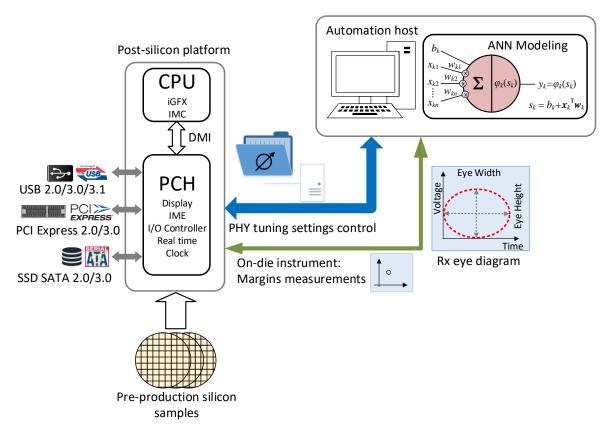

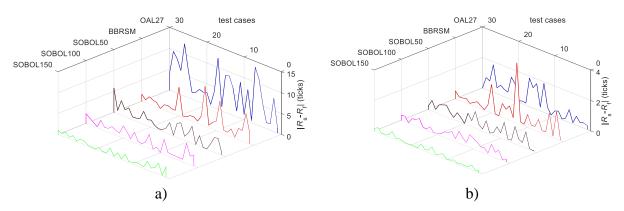

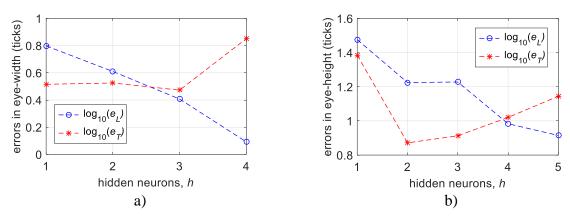

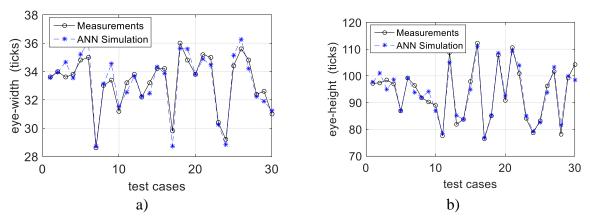

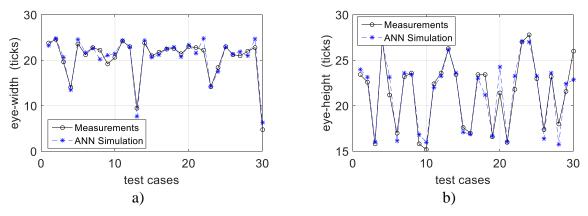

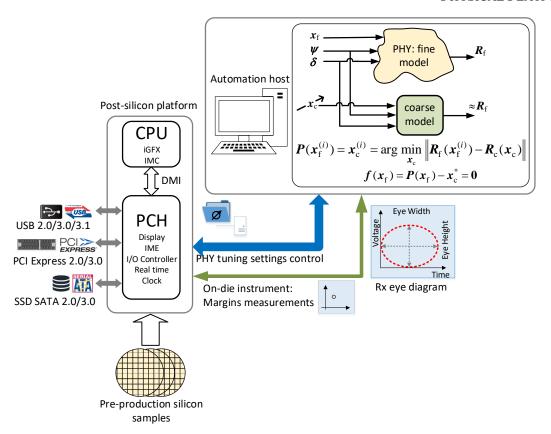

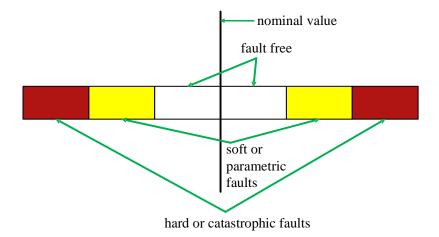

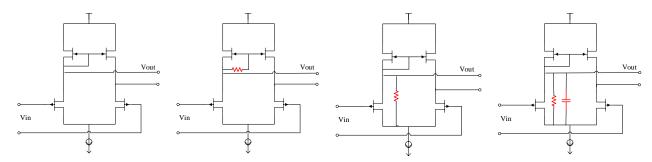

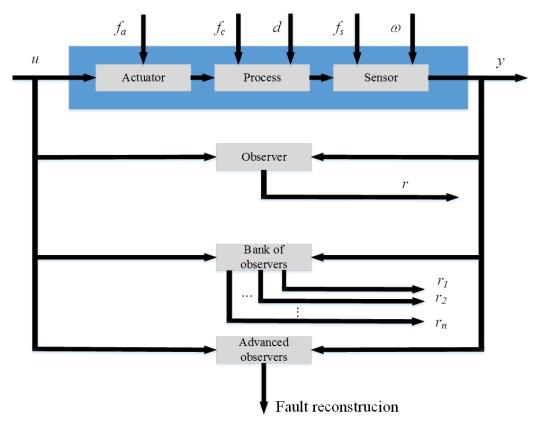

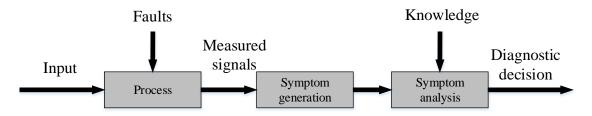

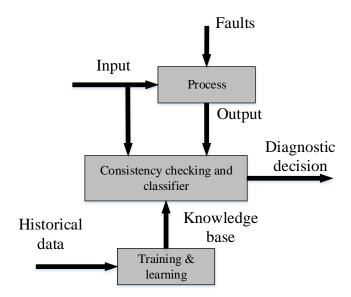

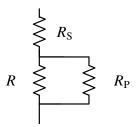

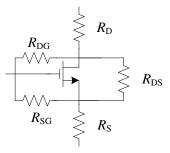

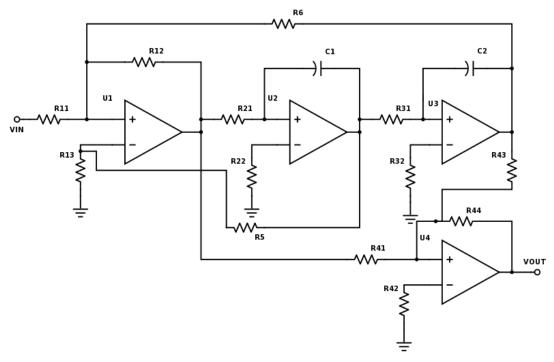

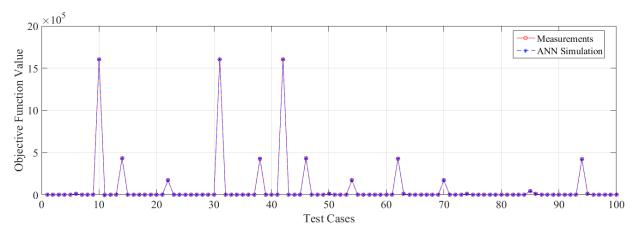

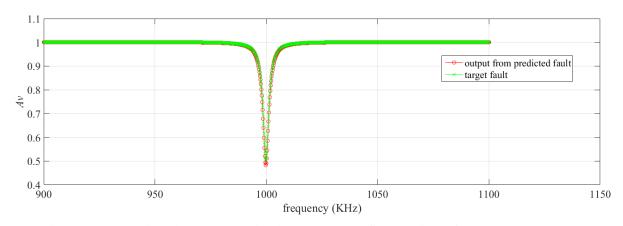

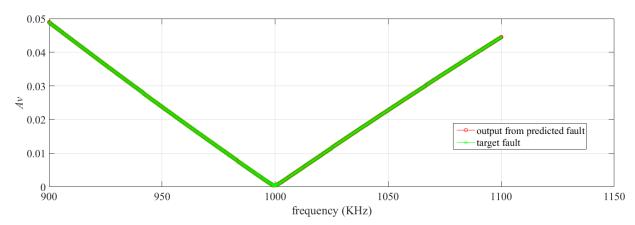

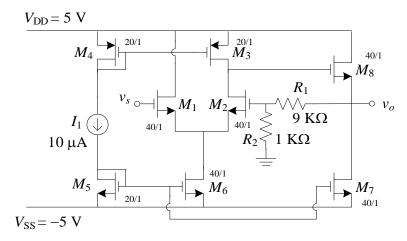

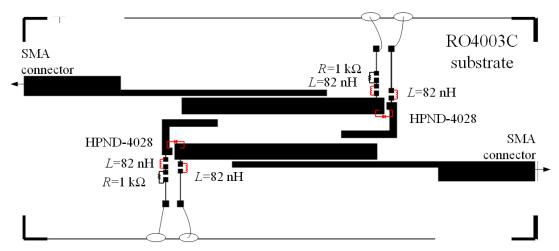

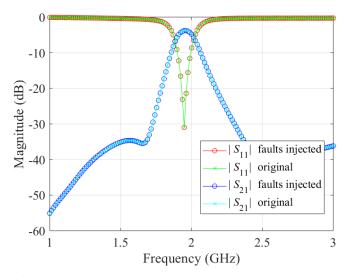

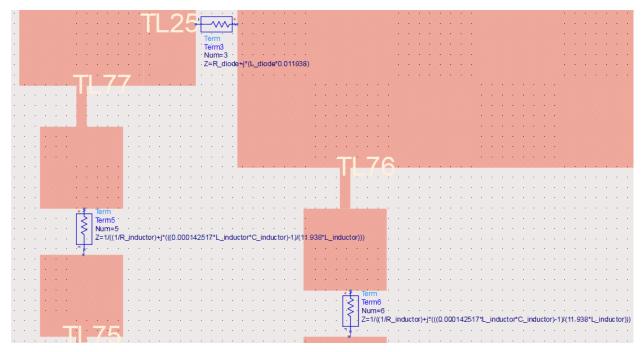

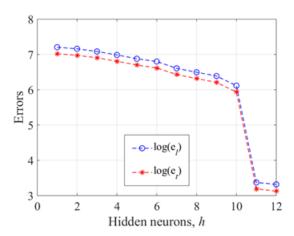

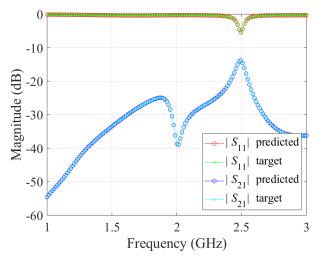

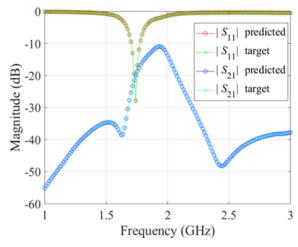

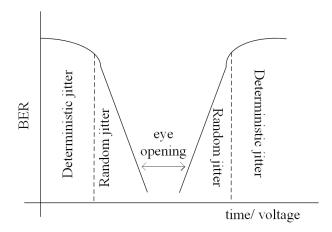

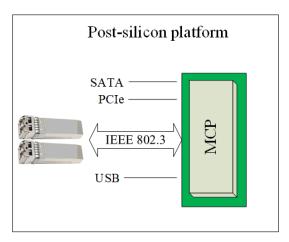

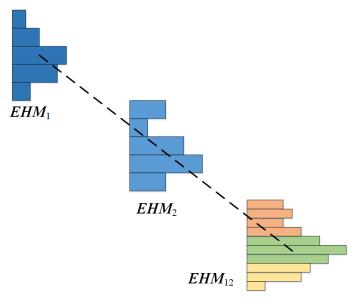

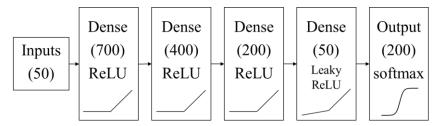

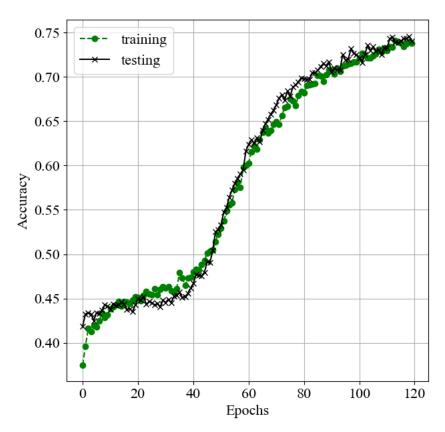

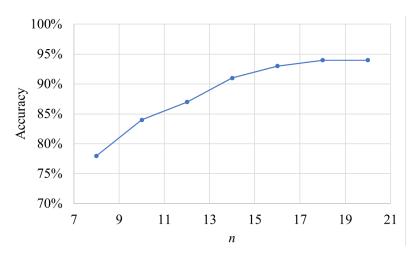

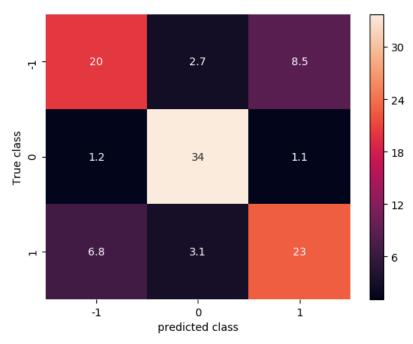

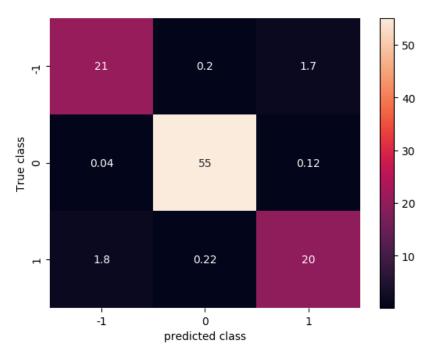

|    | 3.8.  | HYBRID FAU                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | JLT DIAGNOSIS METHODS                             | 66 |