## INSTITUTO TECNOLÓGICO Y DE ESTUDIOS SUPERIORES DE OCCIDENTE

Reconocimiento de validez oficial de estudios de nivel superior según acuerdo secretarial 15018, publicado en el Diario Oficial de la Federación el 29 de noviembre de 1976.

Departamento de Electrónica, Sistemas e Informática

DOCTORADO EN CIENCIAS DE LA INGENIERÍA

# DESARROLLO DE UNA HERAMIENTA DE CAD PARA LA GENERACION AUTOMATICA DE BIBLIOTECAS DE *LAYOUT* DE CIRCUITOS ANALOGICOS BASICOS

Tesis que para obtener el grado de DOCTOR EN CIENCIAS DE LA INGENIERÍA presenta: Ismael Lomelí Illescas

Director de tesis: Dr. Sergio Alfredo Solís Bustos Co-director de tesis: Dr. José Ernesto Rayas Sánchez

Tlaquepaque, Jalisco. Diciembre de 2018

DOCTOR EN CIENCIAS DE LA INGENIERÍA (2018) ITESO, Tlaquepaque, Jal., México

| TÍTULO:            | Desarrollo de una herramienta de CAD para la generación<br>automática de bibliotecas de <i>layout</i> de circuitos analógicos<br>básicos |

|--------------------|------------------------------------------------------------------------------------------------------------------------------------------|

| AUTOR:             | Ismael Lomelí Illescas                                                                                                                   |

|                    | Ingeniero en Comunicaciones y Electrónica (Universidad de                                                                                |

|                    | Guadalajara, México)                                                                                                                     |

|                    | Maestro en Diseño Electrónico (ITESO, México)                                                                                            |

|                    |                                                                                                                                          |

| DIRECTOR DE TESIS: | Sergio Alfredo Solís Bustos                                                                                                              |

|                    | Doctorado en Ciencias (INAOE, México)                                                                                                    |

|                    | Maestría en Ciencias (INAOE, México)                                                                                                     |

|                    | Licenciatura en Electrónica (BUAP, México)                                                                                               |

|                    | Gerente de Diseño Fisco (Intel Corporation Campus Zapopan)                                                                               |

NÚMERO DE PÁGINAS: xxv, 112

## ITESO – The Jesuit University of Guadalajara

Department of Electronics, Systems, and Informatics DOCTORAL PROGRAM IN ENGINEERING SCIENCES

## DEVELOPMENT OF A CAD TOOL FOR THE AUTOMATIC GENERATION OF COMMON ANALOG LAYOUT STRUCTURES AND LIBRARIES

Thesis to obtain the degree of DOCTOR IN ENGINEERING SCIENCES Presents: Ismael Lomeli-Illescas

Thesis Director: Dr. Sergio Alfredo Solís-Bustos Thesis Co-director: Dr. José Ernesto Rayas-Sánchez

> Tlaquepaque, Jalisco, Mexico December 2018

PhD in Engineering Sciences (2018)

| TITLE:           | Development of a CAD Tool for the Automatic Generation     |

|------------------|------------------------------------------------------------|

|                  | of Common Analog Layout Structures and Libraries           |

|                  |                                                            |

| AUTHOR:          | Ismael Lomeli-Illescas                                     |

|                  | Bachelor's degree in communications and electronics        |

|                  | engineering (Universidad de Guadalajara, Mexico)           |

|                  | Master's degree in electronics design (ITESO, Mexico)      |

|                  |                                                            |

|                  |                                                            |

|                  |                                                            |

| THESIS DIRECTOR: | Sergio Alfredo Solís-Bustos                                |

|                  | Physical Design Manager (Intel Corporation Campus Zapopan) |

|                  | Bachelor's degree in electronics (BUAP, Mexico)            |

Master's degree in electronics (INAOE, Mexico) Ph.D. degree in electronics (INAOE, Mexico)

NUMBER OF PAGES: xxv, 112

This work is dedicated to my father, Ismael, and my mother, Araceli, for their understanding, patience, and the continuous loving support they gave me during all the time that this important project in my life lasted.

### Resumen

La implementación física o "layout" de circuitos analógicos es una parte crítica en el proceso de diseño de circuitos integrados (CI). El "layout" de circuitos analógicos en tecnologías de fabricación nanométricas típicamente utiliza transistores con características digitales, lo cual impone uno de los principales desafíos en el diseño de CI debido a las limitaciones en las dimensiones del transistor (restringidas a la utilización de múltiplos de los valores mínimos de longitud y ancho de dichas tecnologías). Además, los circuitos analógicos deben cumplir con especificaciones muy estrictas de diseño, tales como: operación a alta frecuencia, bajo nivel de ruido y alta precisión, las que a su vez dependen de la implementación física. De aquí que la creación apropiada del "layout" es críticamente importante en el desarrollo de CI analógicos. Por otro lado, las herramientas de diseño asistido por computadora (CAD, por sus siglas en inglés) para el diseño físico de CI analógicos están aún lejos de alcanzar un estado de madurez, en contraste con aquellas para el diseño físico de CI digitales. Esto debido a que el diseño analógico es menos sistemático y más heurístico que el diseño digital, por lo que requieren conocimientos y habilidades de diseño más especializados. Adicionalmente, los CI analógicos son más sensibles a perturbaciones, elementos parásitos, interferencia electromagnética, ruido de sustrato y otras fuentes de ruido. Además, existe una amplia diversidad de esquemas para la implementación de cada módulo analógico. Es por ello que la implementación óptima de los diseños analógicos puede requerir muchas iteraciones con la intervención del diseñador experto, e incluso de varios ciclos completos de rediseño, generando ciclos de desarrollo excesivamente largos y costosos. En esta disertación doctoral se presenta una novedosa herramienta de CAD que permite la generación automática de diferentes versiones de "layout" para estructuras analógicas específicas. La herramienta propuesta permite la creación eficiente de múltiples topologías de "layout" para la posterior generación de bibliotecas de dos de las estructuras analógicas más fundamentales: el par diferencial y los dispositivos apilados. Los diseñadores pueden utilizar esta base de datos para el análisis, caracterización y optimización de sus diseños. En la tesis doctoral se presentan análisis de las estructuras mencionadas, así como pruebas que ilustran la funcionalidad y capacidades de la herramienta de CAD propuesta para la creación de dichas bibliotecas de "layout" en un periodo muy corto de tiempo, ayudando a los diseñadores a reducir el ciclo de diseño del circuito.

### **Summary**

The layout implementation of analog circuits has become a critical part of the design process of integrated circuits (IC). The physical construction of this kind of circuits using transistors with digital characteristics as the only devices available in many nanoscale fabrication technologies is one of the main challenges given the limitations in the transistor's dimensions, which are constrained to a multiple of the technology's minimum width and length. In addition to size limitations, analog circuits have to fulfill rigorous design specifications, such as high frequency performance, low noise, and high accuracy, which are strongly dependent on their physical implementation; hence, the optimal layout implementation of the analog circuit becomes of paramount importance in the design process of an integrated circuit. On the other hand, computer-aided design (CAD) tools for analog IC physical design are far from being mature, in contrast to those used for digital IC physical design. Some of the reasons for this are that analog design, in general, is less systematic and more heuristic in nature than digital design. Additionally, analog design often requires specialized knowledge, design skills, and years of experience; analog circuits are more sensitive to parasitic disturbances, EM crosstalk, substrate noise, supply noise, etc.; besides, the variety of schematics and diversity of devices and shapes are much more significant. For all these reasons, the optimal implementation of analog layouts requires several iterations and sometimes rework of the layout, resulting in a very long and expensive developing cycle. In this doctoral dissertation, a novel CAD tool is presented that enables the creation of different layout versions for selected analog structures. The main purpose of the proposed CAD tool is the automatic generation of multiple layout topologies for the subsequent generation of layout libraries or database of two of the most fundamental analog structures: the differential pair and the array of stacked devices. Circuit designers can use this database for the analysis, characterization, optimization, and suitable implementation of their designs. The present doctoral thesis describes several tests and studies for the structures mentioned above, illustrating the functionality and capabilities of the proposed CAD tool for the creation of multiple layout topologies in a very short time, helping designers to reduce the circuit's design cycle.

### Acknowledgements

The author wishes to express his sincere appreciation to Dr. Sergio Alfredo Solis-Bustos, from Intel Corp. campus Zapopan, for his encouragement, expert guidance and keen supervision as doctoral thesis director throughout the course of this work. The author offers his gratitude to Dr. José Ernesto Rayas-Sánchez, Professor of the Department of Electronics, Systems, and Informatics at ITESO, for his reviews and suggestions along the development of the internal research reports, conference and journals papers, as well as for the development of this document.

Author also thanks Dr. Esteban Martínez-Guerrero, Dr. Manuel Salim-Maza, and Dr. Víctor Avendaño-Fernandez, members of his Ph.D. Thesis Committee, for their interest, assessment, and suggestions.

Special thanks are due to Victor Hugo Martinez, formerly from Intel Corp. Zapopan and now at Oracle Guadalajara, for his fruitful cooperation in the development of multiple scripts that enabled the completion of the CAD tool presented in this work.

The author gratefully acknowledge the financial support through a scholarship granted by the *Consejo Nacional de Ciencia y Tecnología* (CONACYT, Mexican Government), as well as, the time flexibility, economic support, and computing tools provided by Intel Corp. campus Zapopan.

Finally, special thanks are due to my family for their understanding, patience, and continuous loving support.

# Contenido

| Re | esume  | en                                                                             | vii   |

|----|--------|--------------------------------------------------------------------------------|-------|

| Su | mma    | nry                                                                            | ix    |

| Re | cono   | cimientos                                                                      | xi    |

| Co | onten  | ido                                                                            | xiii  |

| Co | onten  | ts                                                                             | xix   |

| Li | sta de | e Figuras                                                                      | xxiii |

| Li | sta do | e Tablas                                                                       | XXV   |

| In | trodu  | ıcción                                                                         | 1     |

| 1. |        | itaciones para la Implementación de Layout en Tecno<br>ricación Nanonemetricas | _     |

|    | 1.1.   | LIMITACIONES EN TECNOLOGÍAS NANOMÉTRICAS                                       |       |

|    | 1.2.   | Desafíos en <i>Layouts</i> Analógicos                                          |       |

|    | 1.3.   | MATCHING/ACOPLAMIENTO                                                          |       |

|    |        | 1.3.1 Uso de dispositivos dummies (dumificación)                               |       |

|    |        | 1.3.2 Conexiones al substrato                                                  |       |

|    | 1.4.   | Estructuras de Par Diferencial                                                 |       |

|    | 1.5.   | Estructuras de Transistores Apilados                                           |       |

|    | 1.6.   | Metalización y Ruteo                                                           |       |

|    | 1.7.   | RUTEO EN UNA ESTRUCTURA DE TRANSISTORES APILADOS                               |       |

|    | 1.8.   | REGLAS DE DISEÑO                                                               |       |

|    | 1.9.   | PROPUESTA                                                                      |       |

|    | 1.10   | . Resumen                                                                      |       |

| 2. |      | ilisis del Uso de Transistores Apilados para Aplicaciones Analógi<br>nologías Nanométricas |    |

|----|------|--------------------------------------------------------------------------------------------|----|

|    | 2.1. | EFECTOS SOBRE LAS CURVAS CARACTERÍSTICAS I/V                                               | 30 |

|    | 2.2. | Modulación de la Longitud de Canal                                                         | 32 |

|    | 2.3. | Corriente de Fuga                                                                          | 35 |

|    | 2.4. | Espejo de Corriente                                                                        |    |

|    | 2.5. | TIEMPO DE RETARDO                                                                          | 39 |

|    | 2.6. | RESULTADOS DE SIMULACIÓN                                                                   | 39 |

|    | 2.7  | Resumen                                                                                    | 40 |

| 3. | Her  | ramienta de Síntesis para la Generation Automática de Layout                               | 43 |

|    | 3.1. | DESCRIPCIÓN DE LA HERRAMIENTA                                                              | 44 |

|    | 3.2. | BIBLIOTECAS DE LAS TOPOLOGÍAS                                                              | 46 |

|    |      | 3.2.1 Topologías de par diferencial                                                        | 47 |

|    |      | 3.2.2 Topologías de transistores apilados                                                  | 48 |

|    | 3.3. | Configuración del Ambiente                                                                 | 48 |

|    |      | 3.3.1 Ventana principal                                                                    | 49 |

|    |      | 3.3.2 Análisis de <i>netlist</i>                                                           | 50 |

|    | 3.4. | PARÁMETROS                                                                                 | 51 |

|    |      | 3.4.1 Creación de nuevas celdas                                                            | 51 |

|    | 3.5. | IMPLEMENTACIÓN                                                                             | 52 |

|    |      | 3.5.1 Consideraciones para el <i>layout</i>                                                | 52 |

|    |      | 3.5.2 Validación del número de transistores                                                |    |

|    |      | 3.5.3 Selección de topología                                                               | 53 |

|    |      | 3.5.4 Colocación de dispositivos                                                           | 54 |

|    |      | 3.5.5 Generación de transistores                                                           | 54 |

|    |      | 3.5.6 Algoritmo de control para la colocación de dispositivos                              | 55 |

|    | 3.6. | TERMINACIÓN DEL DISEÑO                                                                     | 57 |

|    | 3.7. | Casos de Prueba                                                                            | 58 |

|    |      | 3.7.1 Par diferencial, caso de prueba 1                                                    | 59 |

|    |      | 3.7.2 Par diferencial, caso de prueba 2                                                    | 62 |

|    |      | 3.7.3 Transistores apilados, caso de prueba 1                                              | 65 |

#### CONTENIDO

| 3.8.   | Resumen y Mejoras                                                                                                             | 67    |

|--------|-------------------------------------------------------------------------------------------------------------------------------|-------|

|        | inición Conceptual de una Herramienta de CAD para la Generación<br>omática de Bibliotecas de Layout de Estructuras Analógicas |       |

| 4.1.   | Descripción General de la Herramienta                                                                                         | 70    |

| 4.2    | CONFIGURACIÓN DE AMBIENTE                                                                                                     | 73    |

| 4.3.   | IMPLEMENTACIÓN                                                                                                                | 73    |

|        | 4.3.1 Creación de nuevas celdas y limpieza                                                                                    | 76    |

|        | 4.3.2 Modificación de parámetros                                                                                              | 76    |

|        | 4.3.3 Número de filas y colocación de dispositivos                                                                            | 77    |

|        | 4.3.4 Reporte de errores                                                                                                      | 78    |

| 4.4.7  | Terminación del Diseño                                                                                                        | 78    |

|        | 4.4.1 Criterios de terminación, bibliotecas y generación de reportes                                                          | 79    |

| 4.5.   | FLUJOS ADICIONALES                                                                                                            | 79    |

|        | 4.5.1 Extracción                                                                                                              | 80    |

|        | 4.5.2 Flujo de LVS                                                                                                            | 80    |

| 4.6.   | CASOS DE PRUEBA                                                                                                               | 81    |

|        | 4.6.1 Generación de bibliotecas                                                                                               | 81    |

|        | 4.6.2 Análisis de elementos parásitos                                                                                         | 83    |

| 4.7.   | Resumen                                                                                                                       | 86    |

|        | l Conclusions                                                                                                                 |       |

| Conciu | siones Generales                                                                                                              | . 91  |

| Apéndi | ce                                                                                                                            | . 95  |

| A.     | Lista de Reportes Internos                                                                                                    | 97    |

| B.     | LISTA DE PUBLICACIONES                                                                                                        | 99    |

| B.1    | Artículos de Congreso.                                                                                                        | 99    |

| B.2    | Artículos de Revista                                                                                                          | 99    |

| C.     | Ejemplos de Reportes Generados                                                                                                | . 101 |

| C.1    | LISTA DE IMPLEMENTACIONES NO VÁLIDAS PARA UN ARREGLO DE TRANSISTORES<br>APILADOS                                              | . 101 |

#### CONTENIDO

| C.2      | LISTA DE IMPLEMENTACIONES NO VÁLIDAS PARA UNA ESTRUCTURA DE PAR<br>DIFERENCIAL | 103 |

|----------|--------------------------------------------------------------------------------|-----|

| Bibliog  | rafía                                                                          | 105 |

| Índice o | le autores                                                                     | 109 |

| Índice o | le términos                                                                    | 111 |

# Contents

| Re | sume    | 2 <i>n</i>                                                | vii   |

|----|---------|-----------------------------------------------------------|-------|

| Su | mma     | nry                                                       | ix    |

| Ac | knov    | vledgements                                               | xi    |

| Со | nten    | ido                                                       | xiii  |

| Co | onten   | ts                                                        | xix   |

| Li | st of ] | Figures                                                   | xxiii |

| Li | st of ' | Tables                                                    | XXV   |

| In | trodu   | iction                                                    |       |

| 1. | IC I    | Layout Limitations in Nanoscale Fabrication Technologies. | 5     |

|    | 1.1.    | LIMITATIONS IN NANOSCALE TECHNOLOGIES                     | 6     |

|    | 1.2.    | ANALOG LAYOUT CHALLENGES                                  | 9     |

|    | 1.3.    | MATCHING                                                  | 9     |

|    |         | 1.3.1 Use of Dummy Devices (Dummification)                |       |

|    |         | 1.3.2 Substrate Connection                                |       |

|    | 1.4.    | DIFFERENTIAL PAIR STRUCTURES                              |       |

|    | 1.5.    | STACKED DEVICES STRUCTURE                                 |       |

|    | 1.6.    | DEVICE METALLIZATION AND ROUTING                          |       |

|    | 1.7.    | ROUTING IN AN ARRAY OF STACKED DEVICES                    |       |

|    | 1.8.    | Design Rules                                              |       |

|    | 1.9.    | PROPOSAL                                                  |       |

|    | 1.10    | . Summary                                                 |       |

| 2. |      | lysis of the Implications of Using Stacked Devices in Analog Circ<br>demented with Nanoscale Technologies |    |

|----|------|-----------------------------------------------------------------------------------------------------------|----|

|    | 2.1. | EFFECTS ON I/V CHARACTERISTICS                                                                            |    |

|    | 2.2. | CHANNEL LENGTH MODULATION                                                                                 |    |

|    | 2.3. | Leakage                                                                                                   |    |

|    | 2.4. | CURRENT MIRROR                                                                                            |    |

|    | 2.5. | Delay Time                                                                                                |    |

|    | 2.6. | CIRCUIT SIMULATION RESULTS SUMMARY                                                                        |    |

|    | 2.7. | SUMMARY                                                                                                   | 40 |

| 3. | Syn  | thesis Tool for Automatic Layout Generation                                                               | 43 |

|    | 3.1. | GENERAL TOOL DESCRIPTION                                                                                  | 44 |

|    | 3.2. | TOPOLOGY LIBRARIES                                                                                        |    |

|    |      | 3.2.1 Differential Pair Topologies                                                                        | 47 |

|    |      | 3.2.2 Stacked Devices Topologies                                                                          |    |

|    | 3.3. | Environment Setting                                                                                       |    |

|    |      | 3.3.1 Main Window                                                                                         | 49 |

|    |      | 3.3.2 Netlist Analysis                                                                                    | 50 |

|    | 3.4. | Read Parameters                                                                                           | 51 |

|    |      | 3.4.1 Cell Creation                                                                                       | 51 |

|    | 3.5. | PLACEMENT IMPLEMENTATION                                                                                  | 52 |

|    |      | 3.5.1 Layout Considerations                                                                               | 52 |

|    |      | 3.5.2 Number of Transistors Validation                                                                    | 52 |

|    |      | 3.5.3 Topology Setting                                                                                    | 53 |

|    |      | 3.5.4 Placement Drawing                                                                                   | 54 |

|    |      | 3.5.5 Transistor Generator                                                                                | 54 |

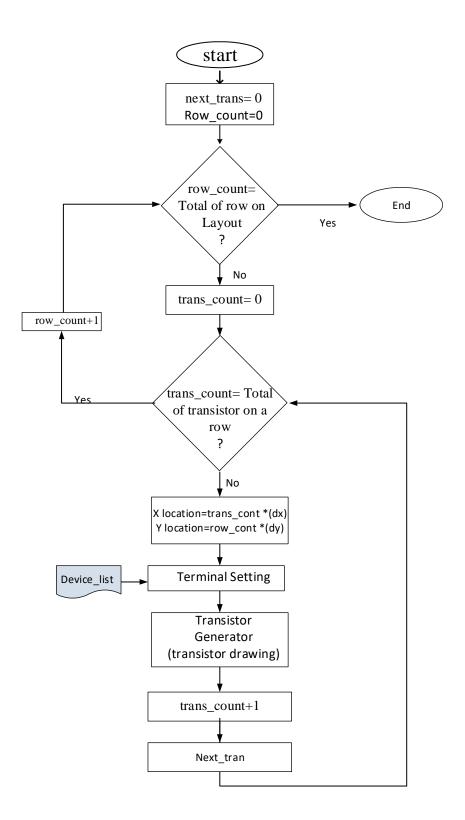

|    |      | 3.5.6 Placement Drawing Control                                                                           | 55 |

|    | 3.6. | LAYOUT COMPLETION                                                                                         | 57 |

|    | 3.7. | ANALYSIS OF THE METALLIZATION ON LAYOUT IMPLEMENTATIONS                                                   | 58 |

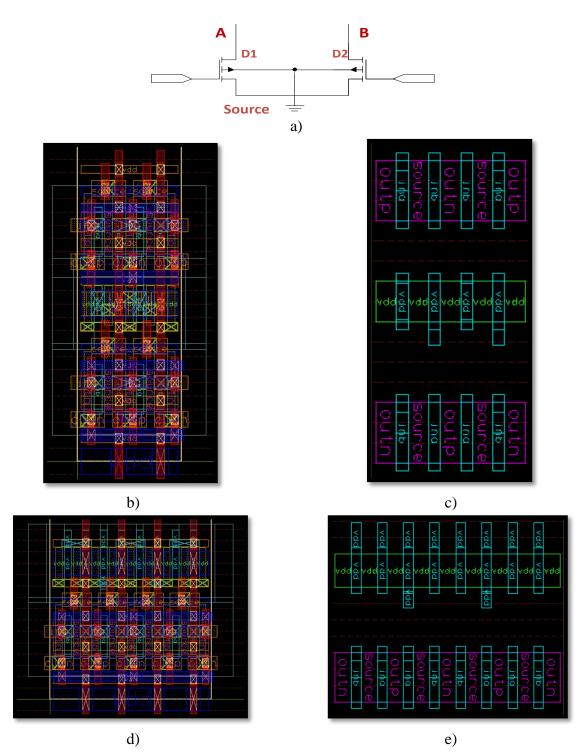

|    |      | 3.7.1 Differential Pair Study Case 1                                                                      | 59 |

|    |      | 3.7.2 Differential Pair Study Case2                                                                       |    |

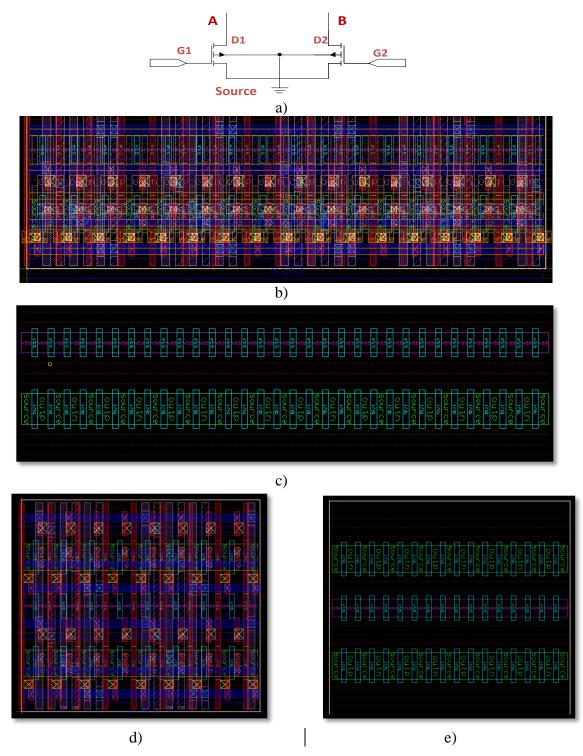

|    |      | 3.7.3 Stacked Devices Study Case1                                                                         |    |

#### CONTENTS

|    | 3.8.        | SUMMARY AND IMPROVEMENTS                                                           | 67  |

|----|-------------|------------------------------------------------------------------------------------|-----|

| 4. |             | D Tool for the Automatic Layout Generation of Libraries of Comn<br>alog Structures |     |

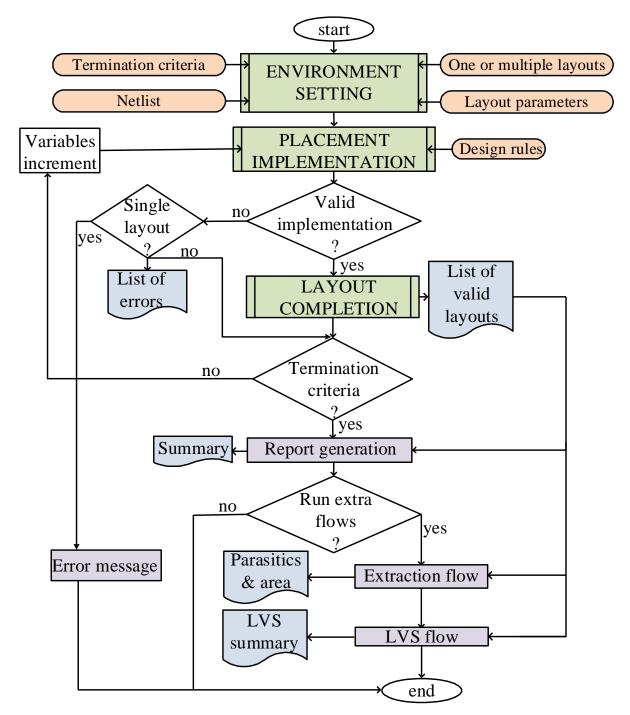

|    | 4.1.        | CAD TOOL GENERAL DESCRIPTION                                                       | 70  |

|    | 4.2.        | Environment Setting                                                                | 73  |

|    |             | 4.2.1 Main Window                                                                  | 73  |

|    | 4.3.        | PLACEMENT IMPLEMENTATION                                                           | 75  |

|    |             | 4.3.1 Cell Creation and Cleaning                                                   | 76  |

|    |             | 4.3.2 Parameters Modification                                                      | 76  |

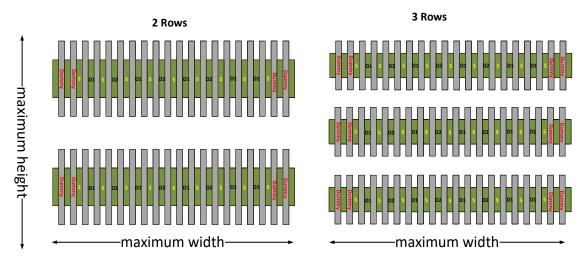

|    |             | 4.3.3 Row Calculation and Placement Drawing                                        | 77  |

|    |             | 4.3.4 Errors Report                                                                | 78  |

|    | 4.4.        | LAYOUT COMPLETION                                                                  | 78  |

|    |             | 4.4.1 Completion Criteria, Database and Report Generation                          | 79  |

|    | 4.5.        | EXTRA FLOWS                                                                        | 79  |

|    |             | 4.5.1 Extraction                                                                   | 80  |

|    |             | 4.5.2 LVS Flow                                                                     | 80  |

|    | 4.6.        | TEST CASES                                                                         | 81  |

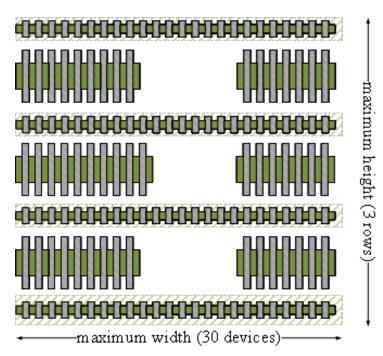

|    |             | 4.6.1 Library Generation                                                           | 81  |

|    |             | 4.6.2 Parasitics Analysis                                                          | 83  |

|    | 4.7.        | SUMMARY                                                                            | 86  |

| Ap | penc        | lix                                                                                | 95  |

|    | A.          | LIST OF INTERNAL RESEARCH REPORTS                                                  | 97  |

|    | B.          | LIST OF PUBLICATIONS                                                               | 99  |

|    | <b>B</b> .1 | CONFERENCES PAPERS                                                                 | 99  |

|    | B.2         | JOURNAL PAPERS                                                                     | 99  |

|    | C.          | EXAMPLES OF ERROR REPORT FILES                                                     | 101 |

|    | C.1         | LIST OF NON-VALID LAYOUT FOR ARRAY OF STACKED DEVICES STRUCTURE                    | 101 |

|    | C.2         | LIST OF NON-VALID LAYOUT FOR THE DIFFERENTIAL PAIR STRUCTURE                       | 103 |

| Bi | bliog       | raphy                                                                              | 105 |

| Author Index  | 109 |

|---------------|-----|

|               |     |

| Subject Index | 111 |

# **List of Figures**

| Fig. 1.1    | Scaling of technology pitch defined by Moore's law                                                                                                                                                                                          |

|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Fig. 1.2    | Illustration of technology pitch: a) transistor top view or layout view, b) transversal cut of the transistor                                                                                                                               |

| Fig. 1.3    | Non-Rectangular Gate (NRG) effect. Example of distortion of a device gate shape                                                                                                                                                             |

| Fig. 1.4    | Variations of temperature caused by a power source: a) illustration of the thermal gradient, b) matching technique of interdigitating, commonly used to mitigate this effect                                                                |

| Fig. 1.5    | Illustrating the Chirality effect                                                                                                                                                                                                           |

| Fig. 1.6    | Ideal dummification. Dummies placed around matched devices to get a similar surrounding environment                                                                                                                                         |

| Fig. 1.7    | Example of substrate connection in a differential pair                                                                                                                                                                                      |

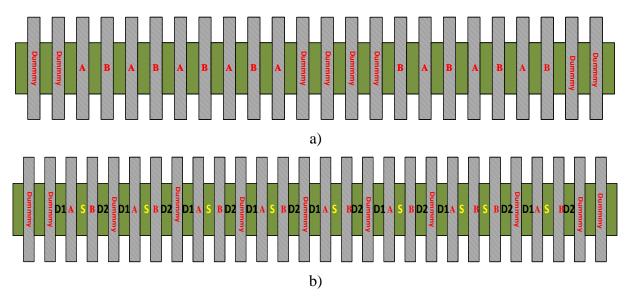

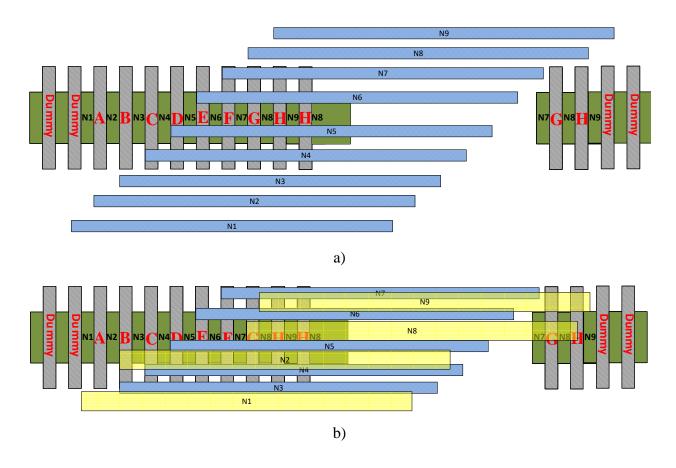

| Fig. 1.8    | Differential pair layout topologies: a) schematic diagram; b) one shared diffusion; c) interdigitated; d) common centroid; e) (gradient) of the square resistance with respect to the distance                                              |

| Fig. 1.9    | Variations of the location of the dummy devices on a layout implementation: a) dummy insertion in the middle of the array, b) interdigitated layout implementation with dummies                                                             |

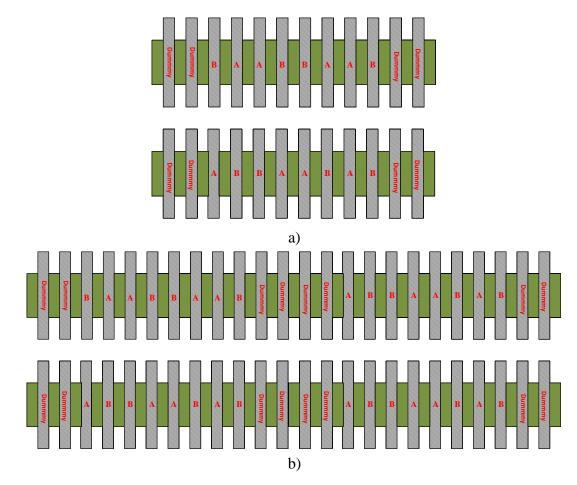

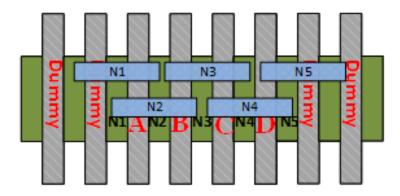

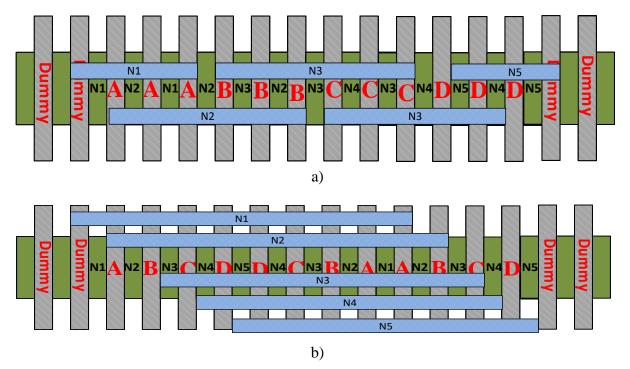

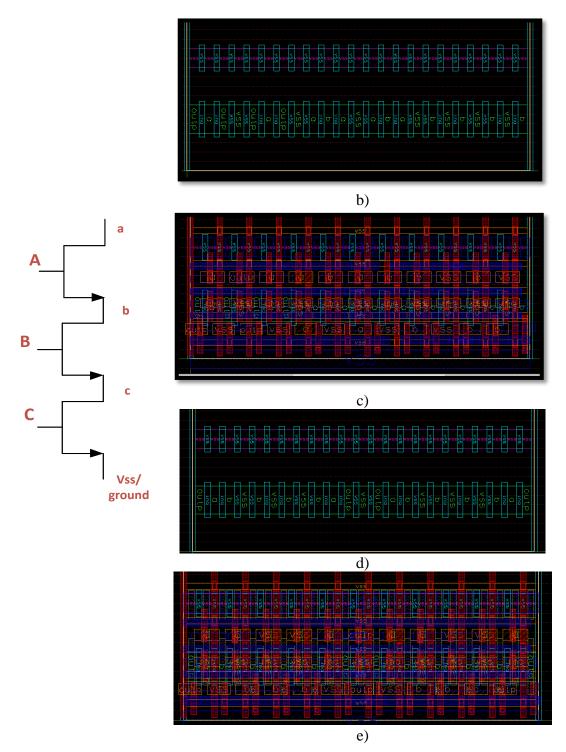

| Fig. 1.10   | Variations on layout implementations: a) two sets (two rows) of transistors array to add gradient tolerance, b) common centroid of interdigitated groups                                                                                    |

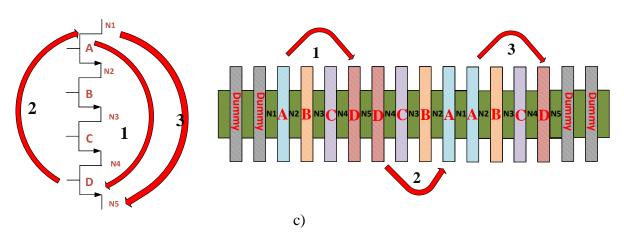

| Fig. 1.11   | Layout topologies for an array of four stacked devices with a different number of fingers per transistor (NFPT): a) schematic diagram; b) one shared diffusion, two cases are shown, NFPT=1 and NFPT=3; c) interdigitated layout, NFPT=3 20 |

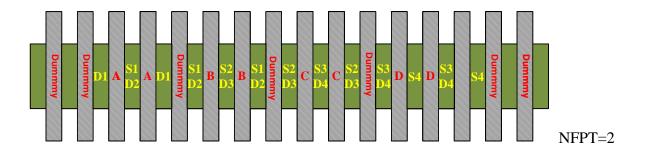

| Fig. 1.12   | Interdigitated Layout implementation of an array of stacked devices with dummy insertion, NFPT=2                                                                                                                                            |

| Fig. 1.13   | Example of metallization over a differential pair                                                                                                                                                                                           |

| Fig. 1.14   | Layout and array of four stacked devices, when the total number of fingers is one                                                                                                                                                           |

| Fig. 1.15   | Comparison between the routing lengths for both topologies: a) one shared diffusion; b) interdigitated layout. The figure is taken from [Lomeli-Illecas-17] 23                                                                              |

| Fig. 1.16 E | Examples of routing for an interdigitated layout topology: a) using the same metal;<br>b) using different metals                                                                                                                            |

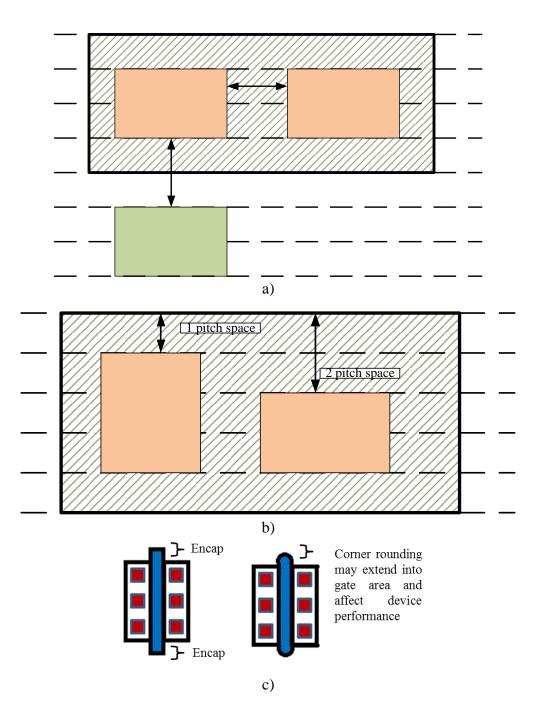

| Fig. 1.17 I | Examples of dimensions that are defined by technology DR: a) space between diffusions b) space from diffusion to n-well c) endcap length                                                                                                    |

### LIST OF FIGURES

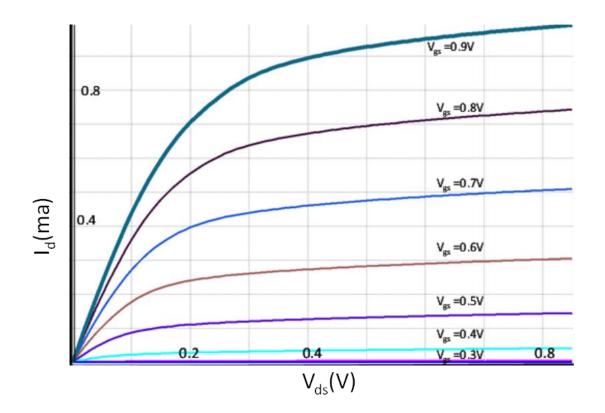

| Fig. 2.1  | Characteristics curves of an NMOS transistor for a given <i>W/L</i> value and multiple values of V <sub>GS</sub>                                                                                                                                                                                                      | . 30 |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| Fig. 2.2  | Characteristics curves of an NMOS transistor for a given $V_{GS}$ value and multiple values of W/L.                                                                                                                                                                                                                   | . 31 |

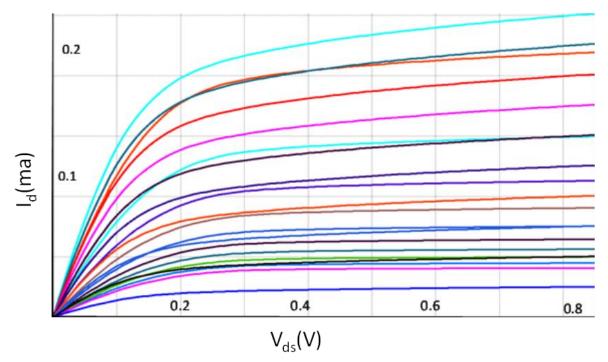

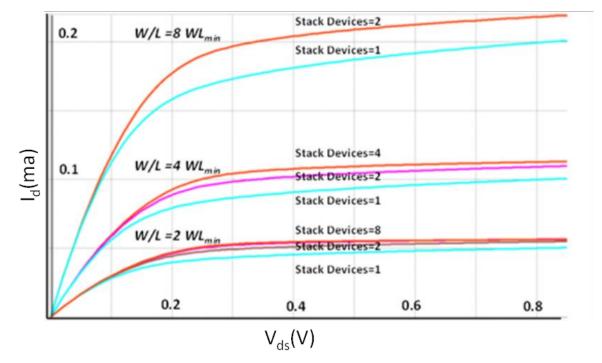

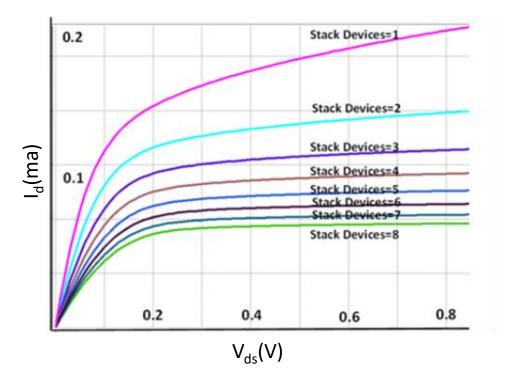

| Fig.2.3   | Characteristics curves of an NMOS transistor for multiple widths and lengths values; stacked devices are used to emulate the variation in the length of the device.                                                                                                                                                   | . 33 |

| Fig. 2.4  | Characteristics curves of an NMOS transistor for multiple $W$ and $L$ values; in each group the $W/L$ ratio is the same, while the values of $W$ and the number of stacked devices change.                                                                                                                            | . 34 |

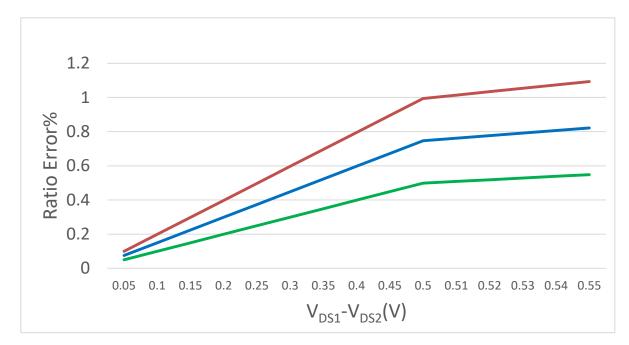

| Fig. 2.5  | Curves of an NMOS transistor in off state for a different number of stacked devices                                                                                                                                                                                                                                   | . 35 |

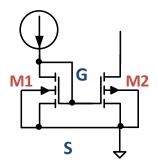

| Fig. 2.6  | Schematic diagram of a simple current mirror                                                                                                                                                                                                                                                                          | . 37 |

| Fig. 2.7  | Percentage of error on current matching for different $\lambda$ values                                                                                                                                                                                                                                                | . 38 |

| Fig. 2.8  | Curves for the output resistance of a simple current mirror using a different<br>number of stack devices                                                                                                                                                                                                              | . 38 |

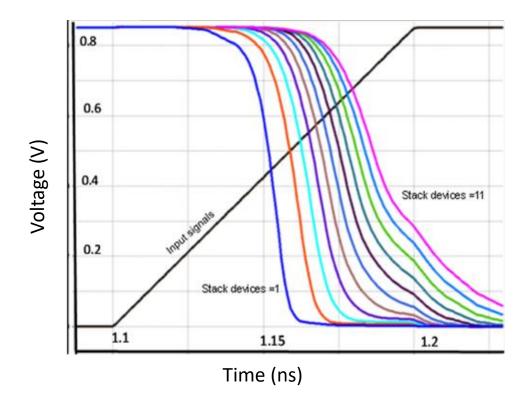

| Fig.2.9   | Curves that illustrate the propagation time for a different number of stack devices in an inverter                                                                                                                                                                                                                    | . 40 |

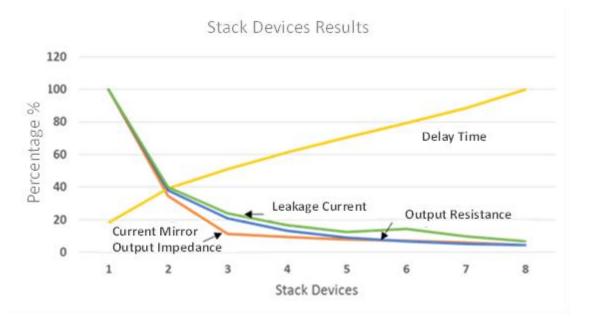

| Fig. 2.10 | Comparison of the reduction for the leakage current, the output resistance for a standalone transistor and for a current mirror and the increase of the delay time for a different number stacked devices.                                                                                                            | . 41 |

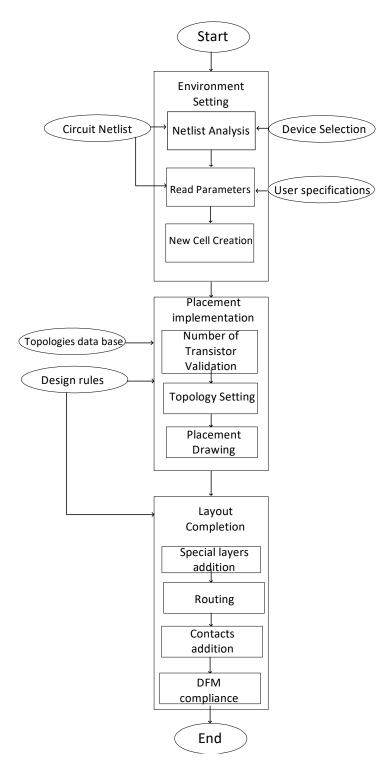

| Fig. 3.1  | Flow diagram of the analog layout synthesis tool                                                                                                                                                                                                                                                                      | . 45 |

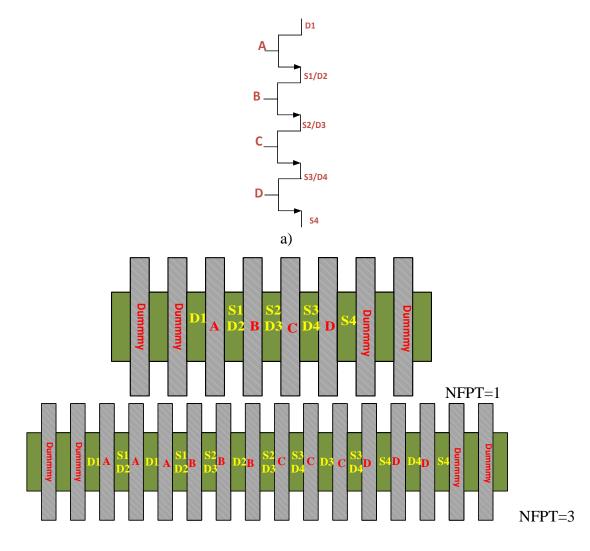

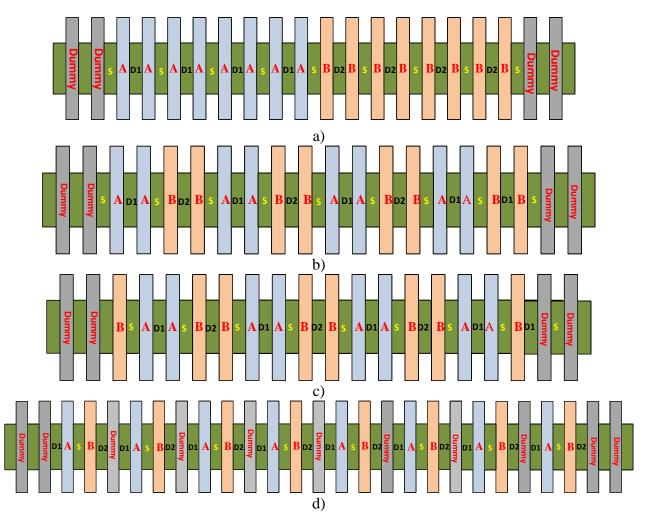

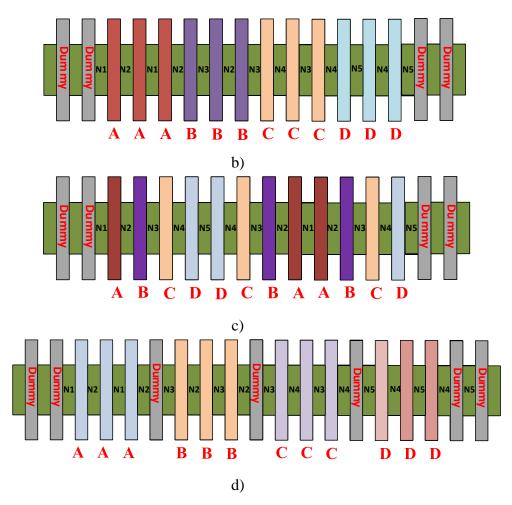

| Fig. 3.2  | Differential pair layout topologies: a) One Shared Diffusion; b) Interdigitated Layout; c) Common Centroid; d) Interdigitated with dummies                                                                                                                                                                            | . 47 |

| Fig. 3.3  | Layout topologies for an array of four stacked devices with a NFPT =3: a) one shared diffusion; b) interdigitated layout; c) interdigitated with dummy insertion.                                                                                                                                                     | . 49 |

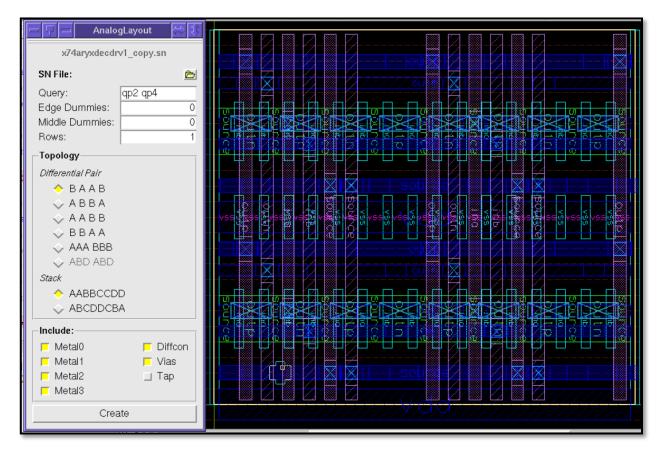

| Fig. 3.4  | Image of the proposed CAD tool and a generated layout example.                                                                                                                                                                                                                                                        | . 50 |

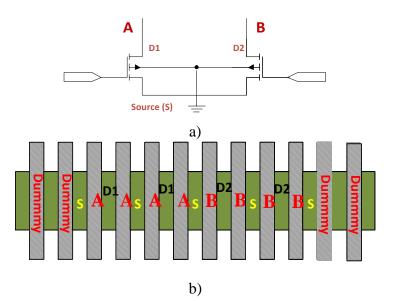

| Fig. 3.5  | Example of placement creation: a) differential pair formed by transistors A and B, each of them with two fingers; b) layout implementation on one row adding two dummy devices and using one source shared topology                                                                                                   | . 53 |

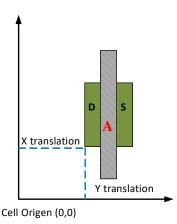

| Fig. 3.6  | Translations on X and Y axis: these parameters specify the exact location where the transistor is drawn.                                                                                                                                                                                                              | . 55 |

| Fig. 3.7  | Flow diagram of the placement drawing algorithm.                                                                                                                                                                                                                                                                      | . 56 |

| Fig. 3.8  | Layout implementation for differential pair circuit formed by PMOS transistors A and B, each of them with 8 fingers using a centroid common topology: a) schematic diagram; b) implementation on one row using all the metallization for interconnection c) placement implementation on one row; d) implementation on |      |

|           | two rows using all the metallization for interconnection e) placement<br>implementation on two rows                                                                                                                                                                                                                                                                                                                          |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Fig. 3.9  | Layout implementation for differential pair circuit formed by NMOS transistors A and B, each of them with 16 fingers using a centroid common topology: a) schematic diagram; b) implementation on one row using all the metallization for interconnection; c) placement implementation on one row; d) implementation on two rows using all the metallization for interconnection d) placement implementation on two rows. 64 |

| Fig. 3.10 | Layout implementation for an array of 3 stacked NMOS transistors, each of them<br>with 4 fingers: a) schematic diagram; b) shared diffusion placement<br>implementation; c) shared diffusion implementation using all the metallization<br>for interconnection; d) interdigitated layout placement implementation; e)<br>interdigitated layout implementation using all the metallization for<br>interconnection             |

| Fig. 4.1  | Flow diagram of the proposed CAD tool for the automatic layout generation of libraries of common analog structures.)Figure taken from [Lomeli-Illescas 18] 71                                                                                                                                                                                                                                                                |

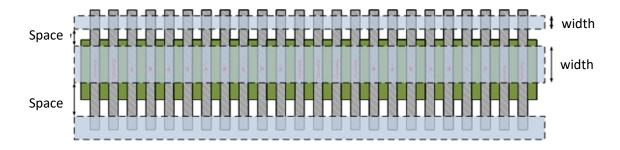

| Fig. 4.2  | Variation of the number of rows, in which the layout is implemented depending<br>on the transistor's width                                                                                                                                                                                                                                                                                                                   |

| Fig. 4.3  | Sample image of the proposed tool with a generated layout75                                                                                                                                                                                                                                                                                                                                                                  |

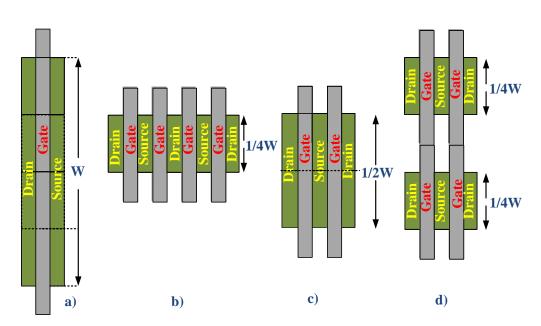

| Fig. 4.4  | Example of transistors finger: a) Transistor A is $W$ wide and uses one finger; b)<br>Transistor A is divided into 4 fingers with a width of $\frac{1}{4}W$ ; c) Transistor A can<br>be divided into 2 fingers with a width of $\frac{1}{2}W$ ; d) Transistor A is split into two<br>transistors of two fingers of $\frac{1}{4}W$ width but placed in two different rows                                                     |

| Fig. 4.5  | Illustration of the area used for the implementation of a sample layout included<br>in the generated libraries                                                                                                                                                                                                                                                                                                               |

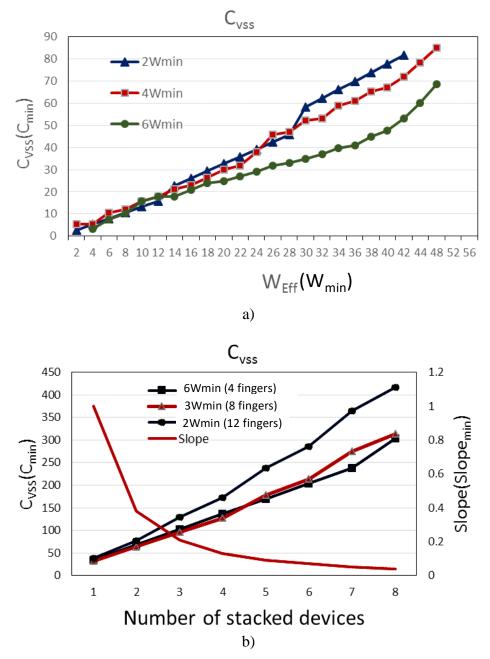

| Fig. 4.6  | Comparison of the Cvss capacitance value for: a) differential pair using different<br>Weff and varying the transistor width; b) array of stacked devices using a<br>different number of transistors and varying the number of fingers;                                                                                                                                                                                       |

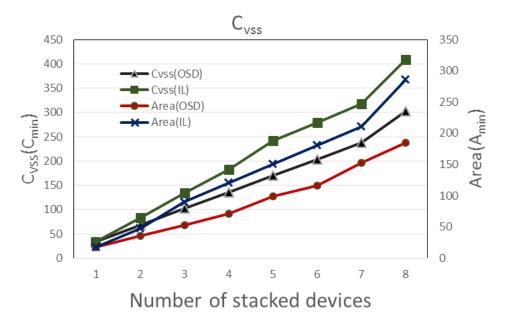

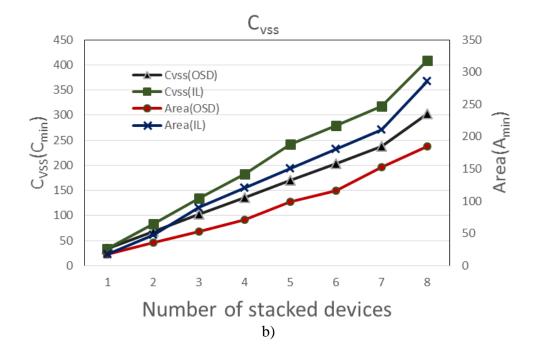

| Fig. 4.7  | Comparison of the $C_{vss}$ capacitance value for using two different topologies: the interdigitated layout (IL) and the one shared diffusion (OSD): a) deferential pair; b) array of stacked devices                                                                                                                                                                                                                        |

# **List of Tables**

| Table 2.1. | SUMMARY OF TRANSISTOR'S IDS CURRENT FOR DIFFERENT                               |    |

|------------|---------------------------------------------------------------------------------|----|

|            | OPTIONS OF W AND L VALUES                                                       | 32 |

| Table 2.2. | SLOPES FOR DIFFERENT W/L RATIOS                                                 | 34 |

| Table 2.3. | RESULTS OF LEAKAGE CURRENT AND DELAY TIME VARYING THE NUMBER OF STACKED DEVICES | 36 |

| Table 2.4. | RESULTS FOR CURRENT MIRROR VALUES VARYING THE NUMBER OF STACKED DEVICES         | 39 |

| Table 3.1. | SUMMARY OF LAYOUT IMPLEMENTATIONS OF A PMOS DIFFERENTIAL PAIR                   | 60 |

| Table 3.2. | SUMMARY OF LAYOUT IMPLEMENTATIONS OF A NMOS DIFFERENTIAL PAIR                   | 63 |

| Table 3.3. | SUMMARY OF LAYOUT IMPLEMENTATIONS OF AN NMOS ARRAY OF THREE STACKED DEVICES     | 67 |

| Table 4.1. | SUMMARY OF RESULTS FOR THE GENERATED LIBRARIES                                  | 83 |

## Introduction

In current nanoscale process technologies (beyond 32 nm), one of the main challenges in the area of the analog circuit design is the implementation of high performance circuits using devices intended for digital applications. The reduction in the power supply voltage, as well as the reduction in transistor's size, impose stringent constraints in analog design, leading to long design time and effort [Ender-09]. In this context, analog layout design is strongly constrained by the transistor's dimensions, connections, and topologies used, and thus the optimal layout implementation becomes critical to achieving the desired high performance of the circuits.

With the usage of nanoscale CMOS technologies, analog designers are facing many new challenges in the layout implementation of the circuits. One of those layout challenges is the severe degradation in device matching characteristics as a consequence of the limitations of actual lithographic techniques: since current device sizes are less than one-quarter of the wavelength of the deep ultraviolet illumination (UV,  $\lambda$ = 193 nm), then more complex interference techniques are necessary for the actual construction of layouts, generating new random variances in layout dimensions. Another example is the high leakage currents resulting from low thresholds and thin gate oxide tunneling currents. In consequence, to accomplish electromigration limits, we require robust metal grids to connect shared-drain analog devices [Lewyn-09]. With all these problems in current layout technologies, the layout implementation become critical, making necessary to have robust layouts, capable of diminishing these effects.

In Chapter 1 the author analyzes the challenges in the implementation of analog circuits in actual nanoscale processes, mostly due to the restrictions in the sizing of the devices: the discretization on the transistor width, and fixed length values. In this same chapter a study of the layout implementation of two well-known circuits: the differential pair and the array of stacked devices is presented.

Chapter 2 presents an in-depth analysis of the implications of the performance of analog circuits due to the use of stacked devices in current nanoscale technologies. To evaluate the use of stacked devices, the characteristic curves of transistors implemented with a different amount of transistors in stack are obtained and compared to those of a single device. Even the analysis of the use of stacked devices is not the main purpose of this work; however, it is important to explain the

#### INTRODUCTION

importance of the use of these structures in the implementation of analog circuits. A similar analysis can be developed for the differential pair structure, however being a well-known structure and for ease of simplicity, this analysis is not presented in this thesis.

The analyses presented in Chapter 1 and Chapter 2 show that even for these basic structures there are several options for their layout implementation, each of them with numerous trade-offs.

In this context, to implement and evaluate different layout placements (or topologies) and analyze their tradeoffs while saving time and layout design resources, it would be very desirable to have a CAD tool that enables fast and efficient implementation of analog layouts while providing useful information on their characteristics for its analysis. However, a fully automated analog design is far from being mature. Analog IC design is still performed mostly manually. Full-custom analog designs lead to long design-test cycles, increasing the time to market and the overall cost [Graeb-09].

Several heuristic placement techniques have been implemented. Among the most popular is the constructive approach, which consists of gradually evolving the placement solution by selecting one module at a time and positioning it in the "best" available location [Graeb-11]. Several CAD systems for analog placement based on constructive methods have been reported [Canaris-91], [Balasa -99]. For instance, a schematic-driven approach employing connectivity and relative positioning in the input schematic is proposed in [Mehranfar-90]. Constructive methods are fast and scale well with the problem size; however, their main drawback is the dependence on the order of selection of the devices [Graeb-11].

Another common technique is based on constraints definition [Graeb-09], used either to define the location and placement of the different devices [Q. Ma-11] or to define the routing paths and, in consequence, the location of the different components [H.-Wu-12]. In general, most of these approaches require intensive user-tool interaction, as well as significant user's experience in analog layout design.

Other useful layout CAD tools are template-driven. These are built on template databases containing analog circuits designed by experienced designers that guide the generation of the new layout [Lourenco-06]. The main disadvantage of this technique is that the generators require considerable coding effort for each new topology [Graeb-11]. Some variations of this approach have been proposed: a CAD tool intended to imitate the constructive layout style of "manual

2

#### **INTRODUCTION**

designers" by generating simple geometries and packing them together into a complex layout is presented in [Lihong-04]; while in [Yilmza-09] the designer directly interacts with the tool at different phases. A performance-constrained parasitic-aware retargeting tool can be found in [Zhang-10]. In [Unutulmaz-10], linear programming is used to generate analog layouts from simple declarative statements, similarly to digital implementations.

All of these implementations require a high level of user intervention for the placement process, and they need from the user considerable expertise in analog layout.

Another one employs the layout retargeting technique that consists of generating a new layout from an existing one. This approach defines the relative position, and the interconnect paths of the devices through the use of templates to guide the generation of the new layout typically used in the design migration from one technology process to a new one [Martins-13]. Examples of the layout retargeting technique are presented in [Mohamed-17], where foundry Parametric Cells (pCells) are used; in [H.-Wu-15], not only layout geometries or building blocks are transferred, but also different constraints from different sources. The retargeting technique allows generating a new layout by acquiring and keeping the design expertise from previous designs. However, it is not very helpful when new layouts with different characteristics are to be implemented, or when different implementations must be compared.

In Chapter 3, the proposed analog layout synthesis tool is presented. The implementation is focused on two of the most commonly used analog building blocks: differential pairs and arrays of stacked devices. Starting from the complete circuit netlist and the names of the selected transistors, our tool verifies that the provided transistors form a valid building block and creates the corresponding layout. The user can define different layout parameters, such as transistor dimensions, number of rows, and number of dummy devices. The layout view can be generated with different levels of detail, including placement of the devices only, basic metals, metallization for complete interconnects, or design for manufacturing (DFM) compliance by adding dummy fills, guard rings. The proposed CAD tool aims at making the full design process more efficient with modern IC fabrication technologies, by providing the circuit designers with quick custom layout views that can be employed to simulate and optimize their designs.

In this same Chapter 3, several tests are presented to show the efficiency and utility of the proposed CAD tool for the generation of the layout of these analog structures, using different configurations and parameters. Also to illustrate how the designer can use the tool, for the analysis

3

#### INTRODUCTION

and comparison of the different layout implementations in terms of their parasitic components an extraction process is performed over the generated layouts.

The different test presented in Chapter 3 illustrates the advantages of the generation of parametric layouts; however, each of these implementations was generated individually (the tool was manually configured for each new layout) and the extraction process was executed individually over each generated layout. Based on the proposed CAD described in Chapter 3, an enhanced CAD tool that enables the creation of a layout database (library) of the aforementioned analog circuit is presented in Chapter4. The primary purpose of the tool is the automatic creation of multiple layout versions of two common analog structures: the differential pair and arrays of stacked devices, for the subsequent generation of a layout library. The proposed CAD tool automatically generates multiple layout versions of these structures. The tool validates all the possible implementations, based on the number of devices and rows; when the layout is a valid one (meaning that it is feasible to implement it with the user input number of rows and devices); it is saved in a database, with its corresponding characteristics. Optionally, an extraction algorithm may be executed over all the elements saved in the database. Finally, the correct implementation of the different layout versions is validated by using a layout versus schematic verification flow. The CAD tool is tested by generating one library for each of the two common analog structures mentioned before. A list of valid and invalid layouts is created as well as the summary of results.

In the general conclusions, the most relevant contributions of the proposed CAD tool are summarized. Additionally, some ideas for future research work are presented. Finally, Appendix A shows the reference list of the eleven internal research reports that the author wrote during his doctoral studies, and Appendix B shows the list of conference and journal papers also published.

## 1. IC Layout Limitations in Nanoscale Fabrication Technologies

The limitations to implement the layout of analog integrated circuits (ICs) in current nanoscale technologies are described in this chapter. Special emphasis is placed on the constraints to size and physically implement transistor's width and length, which are limited to discretized values as multiple of one minimal or reference size, determined by the fabrication technology. Additionally, some of the most important considerations for the layout implementation of reliable analog circuits, which include device matching, metal routing, device interconnection, and design rules are also discussed. Finally, an analysis that considers different options for the layout implementation of two widely used topologies in analog ICs, namely, the differential pair and arrays of stacked transistors is presented. The analysis is intended to show the opportunities that analog layout automation offers for improvement to give circuit designers the capability to test several layout options in less time making the layout design process more efficient and then contribute to the reduction of the IC design cycle and total cost.

In recent years, thanks to the evolution in IC fabrication technologies towards nanoscale CMOS technologies (90, 65, 45nm and beyond), the integration of complex systems, such as network interfaces, wireless designs, telecommunications, and multimedia systems in one single chip, named Systems on Chip (SoC) have been possible [Casier-11]. These integrated systems are increasingly mixed-signal designs, embedding high-performance analog or mixed-signal blocks and possibly sensitive RF frontends together with complex digital circuitry (multiple processors, some logic blocks, and several large memory blocks) on the same chip.

However, the use of CMOS (Complementary Metal Oxide Semiconductor) nanoscale technologies brings significant challenges for mixed signal design that were not encountered before that impact the physical design implementation (layout) of the systems. These challenges include:

- a) The increasing variability of technology parameters, causing mismatch and yield problems.

- b) Aggravating degradation mechanisms (e.g., NBTI-Negative Bias Temperature Instability-Hot Carriers) and increasing reliability constraints such as EMC (Electromagnetic Compatibility) and EMI (Electromagnetic Interference) regulations [Casier-11].

#### 1. IC LAYOUT LIMITATIONS IN NANOSCALE FABRICATION TECHNOLOGIES

In addition to the above challenges, managing the ever-increasing design complexity in tightening time-to-market constraints makes the physical implementation of mixed signal designs and its verification more difficult, highly time-consuming and expensive. In order to enhance designer's efficiency while reducing time and cost different EDA (Electronic Design Automation) methodologies and tools are available for the IC design industry.

While tremendous progress has been made in the digital layout field in recent years, the special characteristics of analog layout design make the development of flexible analog IP (Intellectual Property) blocks a highly difficult task [Saravanan-11].

Some of the main challenges and considerations associated with analog layout design, such as reliability and leakage current problems, were addressed in [Lomelí-Illescas-13]. In this reference, some opportunities for the implementation and improvement of analog layout automation tools are described and they are the source of inspiration for this research work. We base our research on the correct understanding of the constraints and requirements for the implementation and optimization of analog layout through the development of an analog layout automation tool that enables their fast generation and analysis.

In the following section we describe in detail the main limitations found in current nanoscale design technologies.

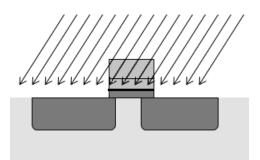

### 1.1. Limitations in Nanoscale Technologies

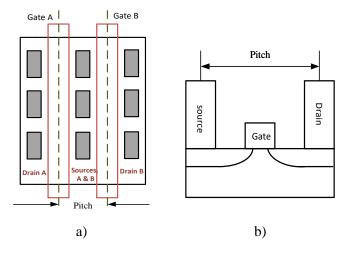

In many old fabrication technologies (micrometers range), the minimal transistor's width was limited by the resolution of the lithographic process, and almost there were no limitations for the maximal transistor's width, except for some practical considerations. In other few cases, the width needed to be a multiple of the device's length. However, in most of the current nanoscale technologies, there is a minimum dimension for the width of the device, which is known as the transistor's pitch (see Fig. 1.2). Larger transistor dimensions need to be a multiple of this pitch. Thus, we can say that in current technologies there is now a discretization of the devices' dimensions. Historically, the pitch scales down around by a factor of 0.7 every two years. This means that the density increases as the pitch decreases by square law. This scaling is sustained by Moore's law, as shown in Fig. 1.2.

#### 1. IC LAYOUT LIMITATIONS IN NANOSCALE FABRICATION TECHNOLOGIES

Fig. 1.1 Illustration of technology pitch: a) transistor top view or layout view, b) transversal cut of the transistor.

Fig. 1.2 Scaling of technology pitch defined by Moore's law.

We also need to consider that transistor's width is not related to its length and even the minimum size is not optimal for the insertion of multiple contacts or vias, which can cause reliability

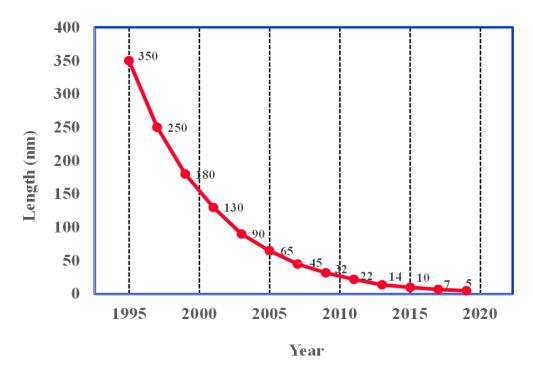

Fig. 1.3 Non-Rectangular Gate (NRG) effect. Example of distortion of a device gate shape.

problems on DC signals or Self Heating<sup>1</sup> (SH) problems on analog or AC signals.

Given all these restrictions in the sizing of the devices, the options for the implementation of analog structures are highly limited, similarly to the implementation of digital circuits, but with the requirements and constraints of the analog ones. In recent technologies, most of the non-desired effects are not exclusive for analog or digital layout implementations, but they are observed in both kinds of circuits [Maricau-13].

The transistor's width has impact on different design and physical parameters, for example, the threshold voltage ( $V_t$ ), transistor's transconductance ( $g_m$ ), and saturation current ( $I_{dsat}$ ) matching. These parameters depend on the precision of many process-driven variables, such as bulk doping concentration,  $V_t$ -shifting implant dose and range, carrier mobility, gate-oxide thickness, and the device W/L dimensional accuracy. However for IC technologies starting at the 100nm node, additional local effects have become significant factors influencing transistor's matching. These effects include  $V_t$  shifts resulting from the proximity of the gate to the N-well edge and  $V_t$  and mobility shifts resulting from the distance to the local trench isolation, among others. At nanoscale technologies, the matching of the devices becomes critical due to secondorder effects related that arise from the reduction of the transistor's dimensions [L. Lewyn-09].

Finally, regular layouts that follow restrictive design rules are essential to have robust CMOS designs to alleviate many manufacturing induced effects, such as the effect of a Non-Rectangular Gate (NRG) due to sub-wavelength lithograph (see Fig. 1.3). NRG dramatically increases the leakage current by more than 15X compared to that of an ideal physical layout; to

<sup>&</sup>lt;sup>1</sup> Self-Heating (Joule Heating) is the rise in temperature of a line as alternating current (AC) flows through it.

mitigate such a penalty, some techniques have been proposed to guarantee regular layout through restrictive design rule parameters [R. Subramaniam-12].

### **1.2.** Analog Layout Challenges

From previous section one of the main challenges in the area of the analog circuit design is the implementation of this kind of circuits using discretized devices; these devices are typically optimized for digital applications. Due to these limitations, an optimal layout implementation is essential to achieve the proper performance of the circuits.

For an optimal layout implementation in a given application, the primary factor that needs to be considered is the matching between devices. However, there are other factors and/or parameters that the designers should address and analyze their contribution on the layout implementation; some of these parameters are the metal routing and its connections (metal layer, contacts or vias, etc.). Similarly, Design Rules (DR) should also be considered; usually, these are not related to a fixed value, but to a range of them, so the election of an optimal value can contribute to diminishing the effect of the non-desired phenomena. These factors are becoming more important in current layout CMOS technologies due to the limitations brought by the scaling on the transistor's minimum size.

### 1.3. Matching

Historically, having proper matching between critical devices is one of the most critical layout design techniques to guarantee the correct functionality of circuits. In analog circuits, matching off voltages and currents is crucial, for example, an 8-bit Video Digital to Analog Converter (DAC) design requires that the current sources match to within +/- 1%; a differential transistor pair circuit typically requires a  $V_t$  mismatch of less than 0.5 mV ( $\approx$ 0.1%).

Device matching in analog and mixed-signal integrated circuits must be carefully considered for high performance and yield. In a typical CMOS process, the absolute accuracy of components such as transistors, capacitors, and resistors varies by as much as 20%, while the parametric ratios may match to within ~0.1%. For this reason, analog circuit implementations typically rely on component matching rather than absolute accuracy. In addition to choosing

#### 1. IC LAYOUT LIMITATIONS IN NANOSCALE FABRICATION TECHNOLOGIES

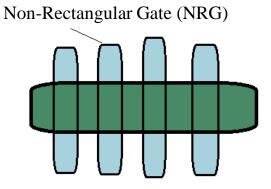

b)

Fig. 1.4 Variations of temperature caused by a power source: a) illustration of the thermal gradient, b) matching technique of interdigitating, commonly used to mitigate this effect.

appropriate transistor dimensions for proper matching, the layout must also be carefully constructed [Ravindranath-98].

However, current technologies have made more difficult to achieve a proper matching: the devices and wires, are closer and the surrounding elements have a more significant effect on them.

Six factors affect transistor matching:

- a) Coincidence: the centroid ("center of gravity") of the matched devices should coincide to minimize the impact of the variation on the different gradients. The gradients (process and temperature) have become critical due to the reduction of dimensions. The illustration of the gradient and an essential technique to mitigate it are shown in Fig. 1.4.

- b) Symmetry: the structure should be symmetric around both the X and Y-axes. It also reduces the impact of gradient variations and enables symmetric routing.

Fig. 1.5 Illustrating the Chirality effect.

- c) Dispersion: the legs of each device should be distributed throughout the array as uniformly as possible to minimize the impact of local variation.

- d) Compactness: the structure should be as compact as possible (ideally a square) to reduce mismatch due to separation.

- e) Proximity (edge effect): each row and column should have an equal number of legs of each device to minimize mismatch from external signal routing or thermal gradient (edges of the array need to be balanced).

- f) Chirality: each device should possess same chirality to minimize the impact of implant angle and orientation-dependent process variation. Chirality is a measure of lefthandedness vs. right-handedness. In other words, each device should have an equal number of legs with source on the left. One form of ideal chirality can be achieved if all legs are arrayed in pairs, as illustrated in Fig. 1.5.

As it can be noticed, the different kinds of gradients affect the matching of the devices. Thus, we may use compact layouts to prevent it, however this could cause thermal effects, as the devices are closer to each other.

Techniques applied heuristically, like dummy devices added on arrays of transistors certainly improve matching but need to be quantified to be implemented correctly. The use of dummy devices is detailed next.

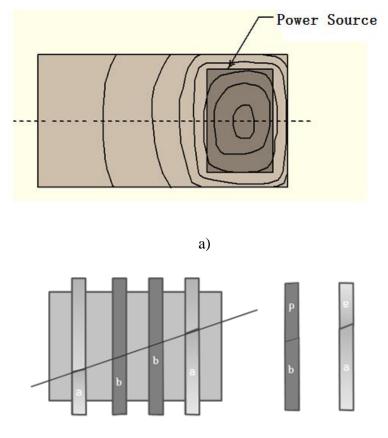

### **1.3.1** Use of Dummy Devices (Dummification)

Many of the characteristics of a layout depend on the surrounding environment. During the

### 1. IC LAYOUT LIMITATIONS IN NANOSCALE FABRICATION TECHNOLOGIES

Fig. 1.6 Ideal dummification. Dummies placed around matched devices to get a similar surrounding environment.

manufacturing process, due to the mechanical polish rates, gas etches rates, material deposit thickness, etc., the device length and width, the implant dose, and the terminal resistance can be impacted; to optimize device matching, each device's environment should be as identical as possible, that is why it is necessary the inclusion of dummy devices at the sides of the transistor arrays, as shown in Fig. 1.6. The use of these dummy transistors is, in consequence, very common but not only for matching purposes of two particular devices but to match the size of a specific section, with another one, inside the complete analog circuit. Furthermore, it is common to add multiple dummy devices to prevent future changes in the design like enhancing current driving capability of the circuit.

The analysis of the different layout topologies could help to optimize the number of dummy transistors and to optimize the area of the layout, avoiding layout rework.

### **1.3.2** Substrate Connection

Another critical parameter for matching nanoscale devices is the substrate connection,

Fig. 1.7 Example of substrate connection in a differential pair.

since matching between closely spaced pairs of devices is influenced primarily by local random and systematic error factors. Matching of devices such as precise capacitors in a large capacitor-DAC (C-DAC) array can be affected by both local and systematic long-distance effects from lithographic patterning several tens of micrometers outside the array, regardless of the technology node. Physical design approaches intended to mitigate these effects in nanoscale technologies are commonly referred as litho-friendly design connection to the substrate [Lewyn-09].

Because nanoscale analog devices are capable of operating at frequencies beyond the 10 GHz range, the location of the substrate ties is a concern in matching differential pairs used in High Frequency (HF) amplifiers. Good device matching and operation at HF requires distance to the well or substrate ties that are uniform and near the source-channel boundary [Lewyn-09].

In the cases described above, substrate connection is another parameter to take in consideration: the location, the size and the wiring of the substrate connection are significant, especially when there are multiple rows in the transistor array. The connection to the substrate should be perfectly matched between the two devices and should consider any possible leakage current. In Fig. 1.7 we can see an example of insertion of substrate connection.

In the following sections, we discuss the two structures under study: the differential pair and stacked devices, as we describe different options for their layouts implementations.

### **1.4. Differential Pair Structures**

The differential pair is shown in Fig. 1.8a. This is one of the most common and critical structures used in different kinds of analog circuits. For this circuit, there are many different layout topologies with different grades of complexity; all of them intended to achieve the best possible matching. Some of the factors that we can compare are the shape of the array of transistors: rectangular or square, which are associated with the number of rows used in the circuit layout. Another aspect that we can take into account is the number of dummy devices and its location: either in the middle or at the fringes of the group; and finally, the symmetry implemented in the transistor array. Next, we describe some possible topologies for the layout implementation of a differential pair

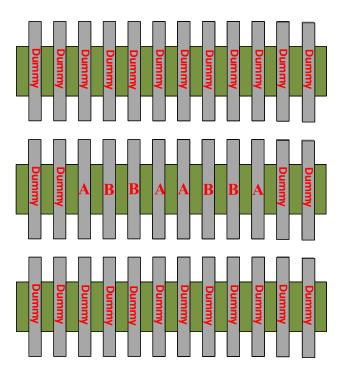

One Shared Diffusion (OSD): This topology is shown in Fig. 1.8b. Here the transistors are divided in fingers and placed one next to each other: all the fingers of the transistor A are placed next to all the fingers of transistor B. Since the transistors share the source connection, they always can be placed together, sharing the diffusion associated to this net. Hence, the number of fingers of the transistors can be an odd or an even number. This topology does not have good matching properties; however, it offers a simple interconnection between the nets.

Interdigitated Layout implementation (IL): Presented in Fig. 1.8c, in this topology, the transistors are also divided in fingers, but in this case, they are placed alternating two fingers of transistor A with two fingers of transistors B. Similarly to the OSD topology, the transistors share the diffusion associated to the source net. Since the fingers of the transistors are placed in pairs, the total number of fingers should be an even number.

Common Centroid (CC) layout implementation: This topology is shown in Fig. 1.8d, it is a variation of the interdigitated layout implementation to improve the gradient tolerance in the horizontal direction. This specific implementation is a unidimensional common centroid implementation, since it is only implemented in one row, however, its main characteristic is its symmetry in the y-direction, even though it has the inconvenient of an asymmetric output load. As in the previous case, the transistors share the diffusion associated with the source net, and the number of fingers should be an even number.

### 1. IC LAYOUT LIMITATIONS IN NANOSCALE FABRICATION TECHNOLOGIES

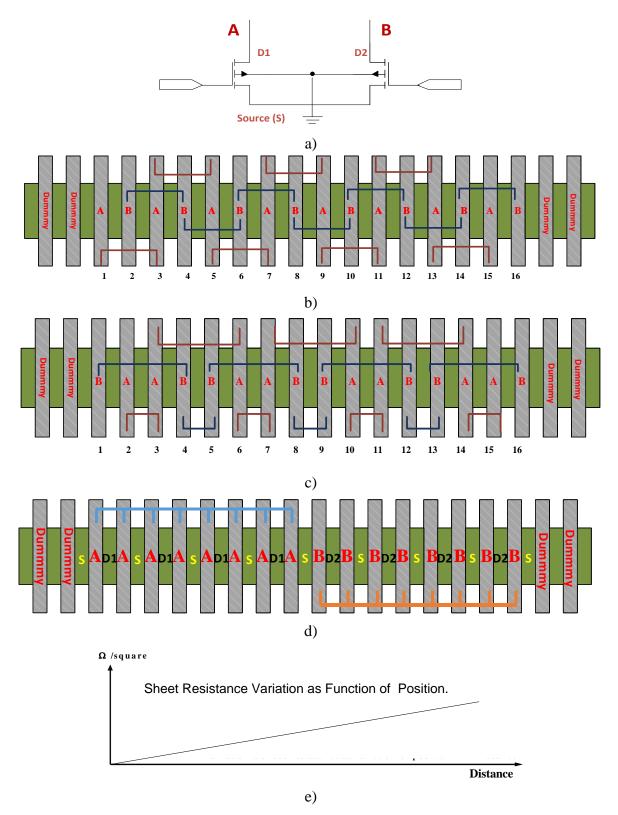

Fig. 1.8 Differential pair layout topologies: a) schematic diagram; b) one shared diffusion; c) interdigitated; d) common centroid; e) variation (gradient) of the square resistance with respect to the distance.

Fig. 1.9 Variations of the location of the dummy devices on a layout implementation: a) dummy insertion in the middle of the array, b) interdigitated layout implementation with dummies.

To illustrate the differences between the three topologies, Fig. 1.8e shows a plot of the variation (gradient) of the square resistance with respect to the distance<sup>2</sup>. Even though the resistance is better balanced in the CC implementation than in the other two topologies as it can be noticed in the connections, the current density is not, since the array has the same transistor at the ends of the array, and the diffusion of this transistor only has half of the current of the other diffusions. As it was addressed the OSD implementation has a poor matching, since all possible variations have a more significant effect in one of the devices (Devices B in Fig. 1.8b), that in the other.

Another possible variable that we can add, in the layout implementation of a differential pair structure is the location of the dummy devices used in the layout. For instance, in all the implementations in Fig. 1.8 the dummy transistors are placed at the sides of the transistor's array, while in Fig. 1.9a there are dummies placed also in the middle. End dummy devices help to improve the matching in the layout, while the middle dummies are used to have a better heat dispersion[S-Shin-16].

Other option is to place the dummy devices between the active transistors: consider the

$<sup>^{2}</sup>$  This plot is a hypothetical example of a linear variation of the material resistance with respect to the distance; it does not represent a physically measured plot. It is used here to illustrate how layout topologies may impact on these variations.

1. IC LAYOUT LIMITATIONS IN NANOSCALE FABRICATION TECHNOLOGIES

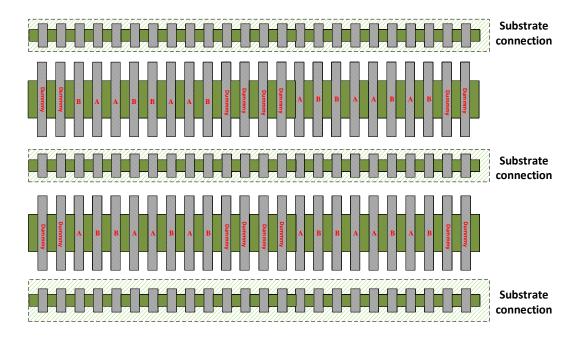

Fig. 1.10 Variations on layout implementations: a) two sets (two rows) of transistors array to add gradient tolerance, b) common centroid of interdigitated groups.