# Analog Fault Identification in RF Circuits using Artificial Neural Networks and Constrained Parameter Extraction

Andrés Viveros-Wacher<sup>1, 2</sup> and José E. Rayas-Sánchez<sup>2</sup>

<sup>1</sup> Intel Corp., Zapopan, Jalisco, 45019 Mexico

<sup>2</sup> Department of Electronics, Systems, and Informatics, ITESO – The Jesuit University of Guadalajara Tlaquepaque, Jalisco, 45604 Mexico

Abstract — The increase of analog and mixed-signal circuitry in modern RF and microwave integrated circuits demands for improved analog fault diagnosis methods. While digital fault diagnosis is well established, the analog counterpart is relatively much less mature due to the intrinsic complexity in analog faults and their corresponding identification. In this work, we present an artificial neural network (ANN) modeling approach to efficiently emulate the injection of analog faults in RF circuits. The resulting meta-model is used for fault identification by applying an optimization-based process using a constrained parameter extraction formulation. The proposed methodology is illustrated by a faulty analog CMOS RF circuit.

Index Terms — analog faults, artificial neural network, gross faults, fault injection, fault identification, parameter extraction.

# I. INTRODUCTION

The growing need of analog and mixed signal integrated circuits (IC) has increased the demand not only of fault tolerance but also of fault detection and isolation [1]. While fault diagnosis techniques for digital circuits are mature and well established, those for analog circuits are still relatively unexplored. This is mainly due to three key points [2]-[4]: a) there are not only two possible signal values, but in principle an infinite number of possible values; b) the timing characteristics of signals are not discrete, but continuous; and 3) the failure mode does not necessarily propagate to the output pins of the circuit.

Analog faults are categorized as catastrophic (or gross) faults and parametric (or soft) faults [5]. Gross faults are typically caused by structural deformities, such as open and short circuits, while parametric faults are generally caused by variations of component parameters outside of their tolerance range. Prior work has used these two types of basic fault models and pursued a fault injection methodology to capture the circuit behavior under faulty conditions [5], [6].

On the other hand, as one of the knowledge-based fault diagnosis methods, machine learning techniques that exploit the use of neural networks have become the most extensively used method for fault diagnosis of many types of systems, including analog circuits [7]-[12]. Most of the previous work focuses on the usage of neural networks as classifiers, to distinguish only between faulty and non-faulty responses [13]-[16]. Other works have used the wavelet transform as preprocessing methods to improve not only the detection but also the isolation of faults [17], [18], namely, the localization of the specific faulty circuit component. However, they require

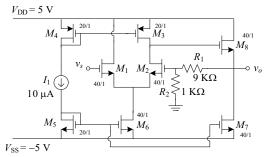

Fig. 1. Original negative feedback CMOS RF amplifier.

complex neural networks as well as prior processing methods to achieve correct identification. This paper proposes using a simple artificial neural network (ANN) to model the effects of injecting gross faults to the circuit under diagnosis. Once the ANN is trained, it is used for fault identification through a simple yet efficient optimization process based on constrained parameter extraction, reproducing a faulty circuit response by optimizing the already trained ANN model inputs. A classical RF CMOS feedback amplifier illustrates our methodology.

# II. ANALOG FAULT MODELS

Analog fault models aim at exposing the circuit under diagnosis to: a) a catastrophic failure, where the circuit cannot operate; b) a performance degradation, where the circuit still works but the performance is lower than its specification; and c) an acceptable performance, despite having the faults. This work employs gross fault models that emulate open and short circuits within the main circuit topology. Opens are modeled by using a high enough value of a serial resistance, while shorts are modeled by using a small enough value of a parallel resistance. The nominal values chosen for the faults in this work are  $200 \text{ M}\Omega$  for opens and  $1 \text{ m}\Omega$  for shorts.

# III. ANALOG FAULT INJECTION ON A CIRCUIT EXAMPLE

The circuit selected for fault injection is a classical CMOS negative feedback RF amplifier depicted Fig. 1, whose nominal voltage gain is shown in Fig. 2.

We inject an open to the drain and source pins of each transistor, and a short between each pair of transistor nodes, in a parametrized manner, in such a way that each fault can be individually activated and have a specific resistive value. When faults are not active, the value used for opens is  $1 \ m\Omega$

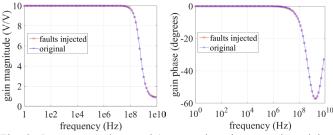

Fig. 2. Response (voltage gain) comparison between the original circuit and the fault-injected circuit with all faults inactive.

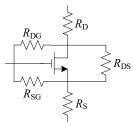

Fig. 3. Five possible faults in a transistor, modeled with opens on the drain  $(R_D)$  and source  $(R_S)$  terminals, and shorts between each pair of terminals  $(R_{DS}, R_{DG} \text{ and } R_{SG})$ .

and for shorts is 200 M $\Omega$ . In this way, we guarantee that under no-fault conditions, the fault-injected circuit behaves as the original circuit, as it is confirmed in Fig. 2.

## IV. ARTIFICIAL NEURAL NETWORK MODELING

# A. Problem Definition

As an initial approach, we aim to neuro-model the behavior of the circuit when injecting a single fault at a time. We define the vector of ANN inputs, x, as follows:  $x_1$  represents the location of the fault, from one out of 8 transistors;  $x_2$  represents one out of the 5 possible faults for each transistor ( $R_D$ ,  $R_S$ ,  $R_{DS}$ ,  $R_{DG}$  and  $R_{SG}$ ), as seen in Fig. 3; and  $x_3$  represents the amount of deviation from the nominal fault value. Given that the faults are analog, their values could take in theory an infinite number of possible values. However, for this work we employ a reduced range from -5% to +5% for  $x_3$ , which is a reasonable manufacturing tolerance.

The output  $\mathbf{R} \in \mathbb{R}^m$  for the ANN model, is defined as

$$\mathbf{R} = \begin{bmatrix} \sum_{i}^{N} \left( \operatorname{Re} \left\{ A v_{i} \right\} - \operatorname{Re} \left\{ A v_{i}^{\operatorname{nf}} \right\} \right) \\ \sum_{i}^{N} \left( \operatorname{Im} \left\{ A v_{i} \right\} - \operatorname{Im} \left\{ A v_{i}^{\operatorname{nf}} \right\} \right) \end{bmatrix}$$

(1)

where  $Av^{nf}$  is the complex amplifier voltage gain when no faults are injected, Av is the gain with the injected fault, and N is the number of sampled frequency points. In other words, the neuro-modeled output represents the deviation of the circuit voltage gain from a no-failure condition.

#### B. ANN Characteristics

We select a 3-layer perceptron for the topology of our ANN. The ANN is implemented and trained using the Matlab neural

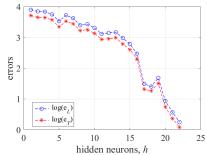

Fig. 4. ANN performance while increasing h, the number of neurons in the hidden layer.

network toolbox. We select the Bayesian regularization algorithm for training, and use 1,000 base points generated using the Sobol pseudo-random sequence to sample the selected solution space as uniformly as possible [19]. Out of the total number of base points, 70% are selected for learning and 30% are selected for testing. The algorithm used for training increases the number of neurons in the hidden layer, h, until the generalization performance deteriorates (similarly to [20]), or until the learning and testing errors are below 1%,

$$(e_{\underline{\text{lold}}} < e_{\underline{\text{lnew}}} \land e_{\underline{\text{lnew}}} > e_{\underline{\text{lnew}}}) \lor (e_{\underline{\text{lnew}}} < 1\% \land e_{\underline{\text{lnew}}} < 1\%)$$

(2)

where  $e_{\text{t_old}}$  is the testing error at the previous iteration and  $e_{\text{t_new}}$  and  $e_{\text{l_new}}$  are the testing and learning errors, respectively, at the current iteration. The ANN performance while increasing h is seen in Fig. 4. The final value of h is 21.

Once the ANN is trained, we test it using 100 extra base points not used during training. The output from the ANN model is compared against actual circuit (SPICE) simulations. The ANN can closely predicts the circuit faulty response, with around 0.00635% of maximum relative error.

# V. FAULT IDENTIFICATION BY PARAMETER EXTRACTION

Here we exploit parameter extraction (PE) as an optimization problem that aims at minimizing the difference between a target response and the system response being optimized [21]. In our work, we aim at finding the input values x of the ANN model that minimize the difference between the objective function value of a faulty circuit, calculated in (1) and treated as the target, and the ANN output. The optimization procedure is executed by solving

$$z^* = \arg\min_{z} \left\| \mathbf{R}(z) - \mathbf{R}^t \right\|_1 \tag{3}$$

where R(z) is the ANN model output and  $R^t$  is the target output. In our case, (3) is solved by using the Nelder-Mead method. In order to keep x, the ANN inputs, within feasible values during the optimization iterations, we use box constraints defined as

$$\mathbf{x} = \begin{bmatrix} x_1^{1b} + (x_1^{ub} - x_1^{1b})(\sin z_1)^2 \\ x_2^{1b} + (x_2^{ub} - x_2^{1b})(\sin z_2)^2 \\ \sin z_3 \end{bmatrix}$$

(4)

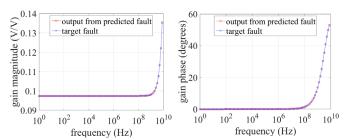

Fig. 5. Comparison between the circuit responses at predicted fault and those at the actual fault injected (gain magnitude and phase).

where  $x_1^{lb} = 1$  and  $x_2^{ub} = 8$  are the selected lower and upper values, respectively. Similarly,  $x_1^{lb} = 1$  and  $x_2^{ub} = 5$  correspond to the upper and lower values for  $x_2$ .

Given the expected high number of local minima, and to overcome the issue of different faults yielding a similar response, we use a statistical PE algorithm, where the starting point of the optimization procedure is slightly perturbed each time the normalized difference between the optimal ANN response and the target response is larger than a desired value,  $\varepsilon_{PE}$ . In our case, the value selected is  $\varepsilon_{PE} = 1 \times 10^{-5}$ .

# C. Fault Identification Results

To validate the effectiveness of our proposal, we select a random fault as target, and followed the PE procedure. The values of x for the actual faults are [2 3 0.1498%]. The resulting values of x match exactly on  $x_1$  and  $x_2$ , thus the fault location within the circuit and the fault type (one out of five possible faults) are identified precisely on each case. There is, however, a slight variation between the predicted (0.02967%) and the actual value in the variable corresponding to the deviation from the nominal fault value,  $x_3$ . Nevertheless, the simulated outputs from the circuit with the identified fault closely resemble the outputs with the original injected fault, as shown in Fig. 5. This consistency was verified for other 5 cases of different injected faults, observing a similar behavior.

# VI. CONCLUSION

An analog gross fault diagnosis method based on artificial neural networks and constrained parameter extraction was proposed in this paper. Our method was illustrated by injecting analog gross faults in a CMOS RF negative feedback amplifier. The gross faults were modeled as resistances with a high enough value in series to cause an open circuit and with a low enough value in parallel to cause a short circuit. The ANN reached the desired learning and generalization performance using 21 neurons at the hidden layer. The ANN was then used as a metamodel, with an extremely low computational cost, to automatically identify faults through a statistical constrained parameter extraction process. Following this process, we were able to properly identify the actual injected faults.

## REFERENCES

- [1] Z. Gao, C. Cecati, and S. X. Ding, "A survey of fault diagnosis and fault-tolerant techniques—Part I: Fault diagnosis with model-based and signal-based approaches," *IEEE Trans. on Ind. Electron.*, vol. 62, no. 6, pp. 3757-3767, Jun. 2015.

- [2] J. W. Bandler and A. E. Salama, "Fault diagnosis of analog circuits," in Proc. IEEE, vol. 73, pp. 1279–1325, Aug. 1985.

- [3] P. Kabisatpathy, A. Barua, and S. Sinha, Fault Diagnosis of Analog Integrated Circuits, New York, NY: Springer, 2005.

- [4] R. Liu, Testing and Diagnosis of Analog Circuits and Systems. New York: Van Nostrand Reinhold, 1991

- [5] D. Bhatta, I. Mukhopadhyay, S. Natarajan, P. Goteti, and B. Xue, "Framework for analog test coverage," in *Int. Symp. on Quality Electronic Design (ISQED)*, Santa Clara, CA, 2013, pp. 468-475.

- [6] M. B. Yelten, S. Natarajan, B. Xue, and P. Goteti, "Scalable and efficient analog parametric fault identification," in *IEEE/ACM Int. Conf. on Computer-Aided Design (ICCAD)*, San Jose, CA, 2013, pp. 387-392.

- [7] L. Chunlai, Z. Xianshuang, and Gudake, "A survey of online fault diagnosis for PV module based on BP neural network," in *Int. Conf. on Smart City and Systems Engineering (ICSCSE)*, Hunan, China, Nov. 2016, pp. 483-486.

- [8] K. Madani, "A survey of artificial neural networks based fault detection and fault diagnosis techniques," in *Int. Joint Conf. on Neural Networks* (*IJCNN*), Washington, DC, Jul. 1999, pp. 3442-3446.

- [9] H. Ma, D. Xu, and Y-S. Lee, "Fault diagnosis of power electronic circuits based on neural network and waveform analysis," in *Proc. of the IEEE Int. Conf. Power Electronics and Drive Systems (PEDS-1999)*, Hong Kong, Jul. 1999, pp. 234-237.

- [10]S. Yang, W. Li, and C. Wang, "The intelligent fault diagnosis of wind turbine gearbox based on artificial neural network," in *Int. Conf. on Condition Monitoring and Diagnosis*, Beijing, Apr. 2008, pp. 1327-1330.

- [11]H. A. Talebi and K. Khorasani, "A neural network-based actuator gain fault detection and isolation strategy for nonlinear systems," in 46th IEEE Conf. Decision Control, New Orleans, LA, Dec. 2007, pp. 2614-2619.

- [12] J-Z. He, Z-H. Zhou, X-R. Yin, and S-F. Chen, "Using neural networks for fault diagnosis," in *Proc. of the Int. Joint Conf. on Neural Networks* (*IJCNN*), Como, Italy, Jul. 2000, pp. 217-220.

- [13]S. Chakrabarty, V. Rajan, J. Ying, M. Mansjur, K. Pattipati, and S. Deb, "A virtual test-bench for analog circuit testability analysis and fault diagnosis," in *Proc. IEEE Syst. Readiness Tech. Conf. Test Technology* for the 21st Century, Salt Lake City, UT, Aug. 1998, pp. 337-352.

- [14]D. Grzechca and J. Rutkowski, "Use of neural network and fuzzy logic to time domain analog tasting," in *Proc. of the 9th Int. Conf. on Neural Inform. Processing*, 2002. ICONIP '02, Nov. 2002, vol. 5, pp. 2601-2604.

- [15]Z. R. Yang, M. Zwolinski, C. D. Chalk, and A. C. Williams, "Applying a robust heteroscedastic probabilistic neural network to analog fault detection and classification," in *IEEE Trans. Computer-Aided Design of Integrated Circuits and Systems*, vol. 19, no. 1, pp. 142-151, Jan. 2000.

- [16] V. Rajan, Jie Yang, S. Chakrabarty, and K. Pattipati, "Machine learning algorithms for fault diagnosis in analog circuits," in *IEEE Int. Conf. Syst., Man, Cybernetics*, San Diego, CA, Oct. 1998, pp. 1874-1879, vol. 2

- [17]S. Guoming, L. Qi, L. Gang, J. Shuyan, and W. Houjun, "Analog circuit fault diagnosis using wavelet feature optimization approach," in 12th IEEE Int. Conf. on Electronic Measurement & Instruments (ICEMI), Qingdao, Jul. 2015, pp. 119-124.

- [18] M. Li, Y. He, L. Yuan, and M. Li, "Fault diagnosis of analog circuit based on wavelet neural networks and chaos differential evolution algorithm," in *Int. Conf. on Electrical and Control Engineering*, Wuhan, Nov. 2010, pp. 986-989.

- [19]I. M. Sobol, "On the distribution of points in a cube and the approximate evaluation of integrals," *U.S.S.R. Computational Mathematics and Mathematical Physics*, vol. 7, pp. 86-112, 1967.

- [20]J. E. Rayas-Sánchez and V. Gutiérrez-Ayala, "EM-based Monte Carlo analysis and yield prediction of microwave circuits using linear-input neural-output space mapping," *IEEE Trans. Microwave Theory Techn.*, vol. 54, no. 12, pp. 4528-4537, Dec. 2006.

- [21] J. E. Rayas-Sanchez, "Power in simplicity with ASM: tracing the aggressive space mapping algorithm over two decades of development and engineering applications," *IEEE Microwave Magazine*, vol. 17, no. 4, pp. 64-76, Apr. 2016.